# Bridgetek Pte Ltd FT81x (0/1/2/3)

(Advanced Embedded Video Engine)

The FT81x is a series of easy to use graphic controllers targeted at embedded applications to generate high-quality Human Machine Interfaces (HMIs). It has the following features:

- Advanced Embedded Video Engine(EVE) with high resolution graphics and video playback

- FT81x functionality includes graphic control, audio control, and touch control interface.

- Pinout backward compatible with FT800 (FT810) and FT801 (FT811).

- Support multiple widgets for simplified design implementation

- Built-in graphics operations allow users with little expertise to create high-quality displays

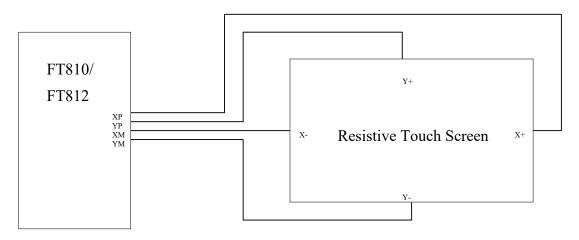

- Support 4-wire resistive touch screen (FT810/FT812)

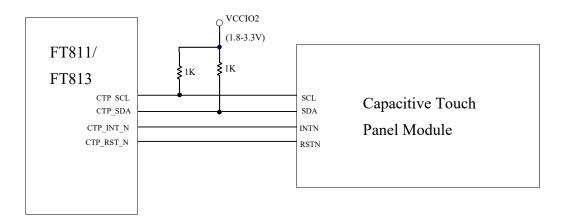

- Support capacitive touch screen with up to 5 touches detection (FT811/FT813)

- Hardware engine can recognize touch tags and track touch movement. Provides notification for up to 255 touch tags.

- Enhanced sketch processing

- Programmable interrupt controller provides interrupts to host MCU

- Built-in 12MHz crystal oscillator with PLL providing programmable system clock up to 60MHz

- Clock switch command for internal or external clock source. External 12MHz crystal or clock input can be used for higher accuracy.

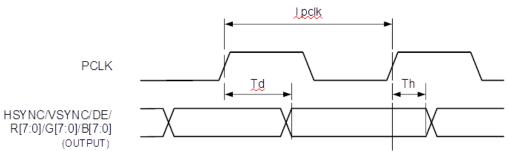

- Video RGB parallel output; configurable to support PCLK up to 60MHz and R/G/B output of 1 to 8 bits

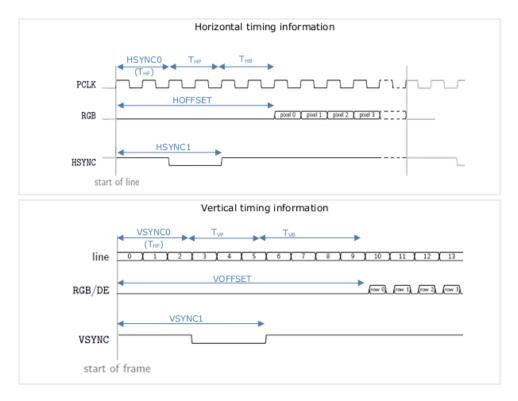

- Programmable timing to adjust HSYNC and VSYNC timing, enabling interface to numerous displays

- Support for LCD display with resolution up to SVGA (800x600) and formats with data enable (DE) mode or VSYNC/HSYNC mode

- Support landscape and portrait orientations

- Display enabled control output to LCD panel

- Integrated 1MByte graphics RAM, no frame buffer RAM required

- Support playback of motion-JPEG encoded AVI videos

- Mono audio channel output with PWM output

- · Built-in sound synthesizer

- Audio wave playback for mono 8-bit linear PCM, 4-bit ADPCM and μ-Law coding format at sampling frequencies from 8 kHz to 48 kHz. Built-in digital filter reduces the system design complexity of external filtering

- PWM output for display backlight dimming control

- Advanced object oriented architecture enables low cost MPU/MCU as system host using SPI interfaces

- Support SPI data lines in single, dual or quad mode; SPI clock up to 30MHz

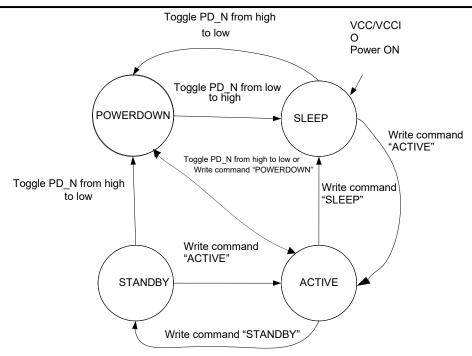

- Power mode control allows the chip to be put in power down, sleep and standby states

- Supports I/O voltage from 1.8V to 3.3V

- Internal voltage regulator supplies 1.2V to the digital core

- Build-in Power-on-reset circuit

- -40°C to 85°C extended operating temperature range

- Available in a compact Pb-free, VQFN-48 and VQFN-56 package, RoHS compliant

Neither the whole nor any part of the information contained in, or the product described in this manual, may be adapted or reproduced in any material or electronic form without the prior written consent of the copyright holder. This product and its documentation are supplied on an as-is basis and no warranty as to their suitability for any particular purpose is either made or implied. Bridgetek Pte Ltd will not accept any claim for damages howsoever arising as a result of use or failure of this product. Your statutory rights are not affected. This product or any variant of it is not intended for use in any medical appliance, device or system in which the failure of the product might reasonably be expected to result in personal injury. This document provides preliminary information that may be subject to change without notice. No freedom to use patents or other intellectual property rights is implied by the publication of this document. Bridgetek Pte Ltd, 1 Tai Seng Avenue, Tower A, #03-05, Singapore 536464. Singapore Registered Company Number: 201542387H.

# 1 Typical Applications

- Point of Sales Machines

- Multi-function Printers

- Instrumentation

- Home Security Systems

- Graphic touch pad remote, dial pad

- Tele / Video Conference Systems

- Phones and Switchboards

- Medical Appliances

- Blood Pressure displays

- Heart monitors

- Glucose level displays

- Breathalyzers

- Gas chromatographs

- Power meter

- · Home appliance devices

- Set-top box

- Thermostats

- Sprinkler system displays

- Medical Appliances

- GPS / Satnav

- Vending Machine Control Panels

- Elevator Controls

- .....and many more

#### 1.1 Part Numbers

| Part Number | Description                           | Package                                 |

|-------------|---------------------------------------|-----------------------------------------|

| FT810Q-x    | EVE with 18 bit RGB, resistive touch  | 48 Pin VQFN, body 7 x 7 mm, pitch 0.5mm |

| FT811Q-x    | EVE with 18 bit RGB, capacitive touch | 48 Pin VQFN, body 7 x 7 mm, pitch 0.5mm |

| FT812Q-x    | EVE with 24 bit RGB, resistive touch  | 56 Pin VQFN, body 8 x 8 mm, pitch 0.5mm |

| FT8130-x    | EVE with 24 bit RGB, capacitive touch | 56 Pin VOFN, body 8 x 8 mm, pitch 0.5mm |

Table 1- FT81x Embedded Video Engine Part Numbers

**Note:** Packaging codes for x is:

-R: Taped and Reel (3000pcs per reel)

-T: Tray packing (260 pcs per tray for VQFN-48, 348 pcs per tray for VQFN-56)

For example: FT810Q-R is 3000 VQFN pieces in taped and reel packaging

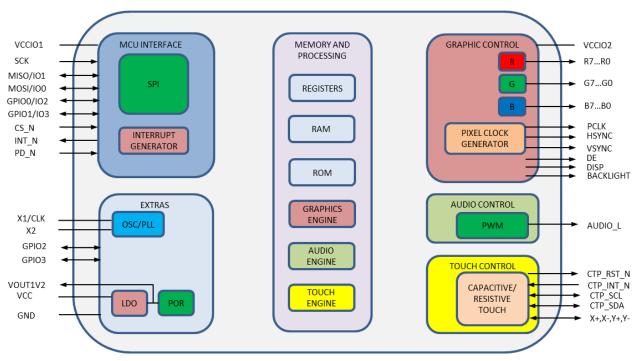

# 2 Block Diagram

Figure 2-1 FT81x Block Diagram

For a description of each function please refer to Section 4.

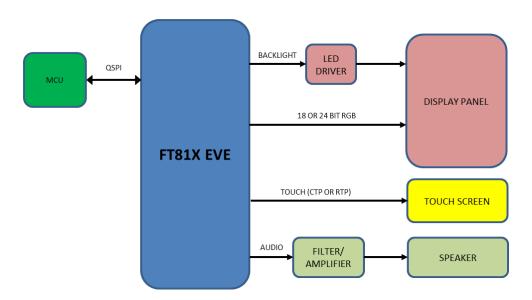

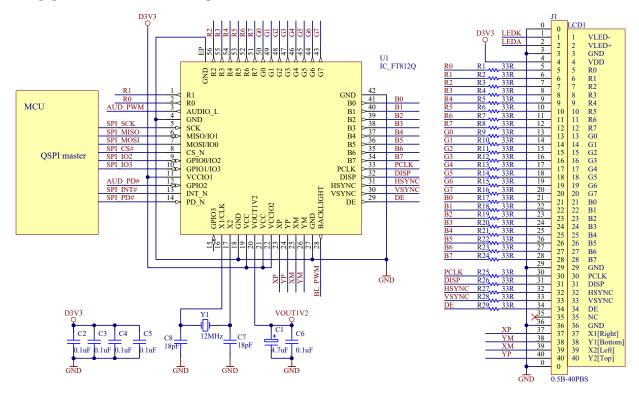

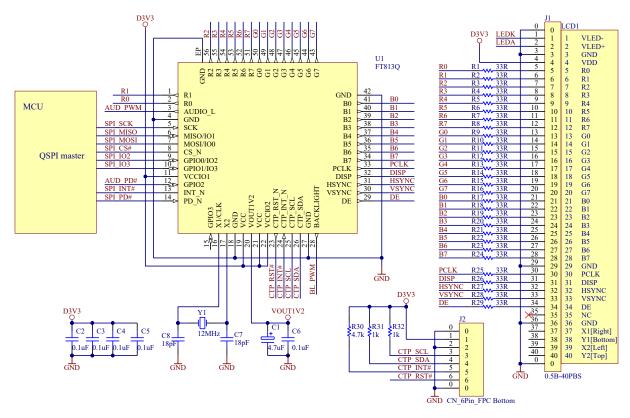

Figure 2-2 FT81x System Design Diagram

FT81x with EVE (Embedded Video Engine) technology simplifies the system architecture for advanced human machine interfaces (HMIs) by providing support for display, audio, and touch as well as an object oriented architecture approach that extends from display creation to the rendering of the graphics.

# **Table of Contents**

| 1.1 Part Numbers  2 Block Diagram  3 Device Pin Out and Signal Description  3.1 FT810 VQFN-48 Package Pin Out  3.2 FT811 VQFN-48 Package Pin Out  3.3 FT812 VQFN-56 Package Pin Out  3.4 FT813 VQFN-56 Package Pin Out  3.5 Pin Description  4 Function Description  1 4.1 Quad SPI Host Interface  4.1.1 QSPI Interface  4.1.2 Serial Data Protocol  4.1.3 Host Memory Read  4.1.4 Host Memory Write  4.1.5 Host Command  4.1.6 Interrupts  4.2 System Clock  1 4.2.1 Clock Source  4.2.2 Phase Locked Loop                                    |           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 3.1 FT810 VQFN-48 Package Pin Out 3.2 FT811 VQFN-48 Package Pin Out 3.3 FT812 VQFN-56 Package Pin Out 3.4 FT813 VQFN-56 Package Pin Out 3.5 Pin Description 4 Function Description 4.1 Quad SPI Host Interface 4.1.1 QSPI Interface 4.1.2 Serial Data Protocol 4.1.3 Host Memory Read 4.1.4 Host Memory Write 4.1.5 Host Command 4.1.6 Interrupts 4.2 System Clock 4.2.1 Clock Source                                                                                                                                                           |           |

| 3.1 FT810 VQFN-48 Package Pin Out 3.2 FT811 VQFN-48 Package Pin Out 3.3 FT812 VQFN-56 Package Pin Out 3.4 FT813 VQFN-56 Package Pin Out 3.5 Pin Description 4 Function Description 4.1 Quad SPI Host Interface 4.1.1 QSPI Interface 4.1.2 Serial Data Protocol 4.1.3 Host Memory Read 4.1.4 Host Memory Write 4.1.5 Host Command 4.1.6 Interrupts 4.2 System Clock 4.2.1 Clock Source                                                                                                                                                           |           |

| 3.1 FT810 VQFN-48 Package Pin Out  3.2 FT811 VQFN-48 Package Pin Out  3.3 FT812 VQFN-56 Package Pin Out  3.4 FT813 VQFN-56 Package Pin Out  3.5 Pin Description  4 Function Description  1 4.1 Quad SPI Host Interface  4.1.1 QSPI Interface  4.1.2 Serial Data Protocol  4.1.3 Host Memory Read  4.1.4 Host Memory Write  4.1.5 Host Command  4.1.6 Interrupts  4.2 System Clock  4.2.1 Clock Source                                                                                                                                           |           |

| 3.2       FT811 VQFN-48 Package Pin Out         3.3       FT812 VQFN-56 Package Pin Out         3.4       FT813 VQFN-56 Package Pin Out         3.5       Pin Description         4       Function Description         4.1       Quad SPI Host Interface         4.1.1       QSPI Interface         4.1.2       Serial Data Protocol         4.1.3       Host Memory Read         4.1.4       Host Memory Write         4.1.5       Host Command         4.1.6       Interrupts         4.2       System Clock         4.2.1       Clock Source |           |

| 3.3 FT812 VQFN-56 Package Pin Out  3.4 FT813 VQFN-56 Package Pin Out  3.5 Pin Description  4 Function Description  1 4.1 Quad SPI Host Interface  4.1.1 QSPI Interface  4.1.2 Serial Data Protocol  4.1.3 Host Memory Read  4.1.4 Host Memory Write  4.1.5 Host Command  4.1.6 Interrupts  4.2 System Clock  4.2.1 Clock Source                                                                                                                                                                                                                 |           |

| 3.4 FT813 VQFN-56 Package Pin Out         3.5 Pin Description         4 Function Description       1         4.1 Quad SPI Host Interface       1         4.1.1 QSPI Interface       1         4.1.2 Serial Data Protocol       1         4.1.3 Host Memory Read       1         4.1.4 Host Memory Write       1         4.1.5 Host Command       1         4.1.6 Interrupts       1         4.2 System Clock       1         4.2.1 Clock Source       1                                                                                         |           |

| 3.5 Pin Description       1         4 Function Description       1         4.1 Quad SPI Host Interface       1         4.1.1 QSPI Interface       1         4.1.2 Serial Data Protocol       1         4.1.3 Host Memory Read       1         4.1.4 Host Memory Write       1         4.1.5 Host Command       1         4.1.6 Interrupts       1         4.2 System Clock       1         4.2.1 Clock Source       1                                                                                                                           |           |

| 4 Function Description       1         4.1 Quad SPI Host Interface       1         4.1.1 QSPI Interface       1         4.1.2 Serial Data Protocol       1         4.1.3 Host Memory Read       1         4.1.4 Host Memory Write       1         4.1.5 Host Command       1         4.1.6 Interrupts       1         4.2 System Clock       1         4.2.1 Clock Source       1                                                                                                                                                               |           |

| 4.1 Quad SPI Host Interface       1         4.1.1 QSPI Interface       1         4.1.2 Serial Data Protocol       1         4.1.3 Host Memory Read       1         4.1.4 Host Memory Write       1         4.1.5 Host Command       1         4.1.6 Interrupts       1         4.2 System Clock       1         4.2.1 Clock Source       1                                                                                                                                                                                                      |           |

| 4.1.1 QSPI Interface       1         4.1.2 Serial Data Protocol       1         4.1.3 Host Memory Read       1         4.1.4 Host Memory Write       1         4.1.5 Host Command       1         4.1.6 Interrupts       1         4.2 System Clock       1         4.2.1 Clock Source       1                                                                                                                                                                                                                                                  |           |

| 4.1.2       Serial Data Protocol       1         4.1.3       Host Memory Read       1         4.1.4       Host Memory Write       1         4.1.5       Host Command       1         4.1.6       Interrupts       1         4.2       System Clock       1         4.2.1       Clock Source       1                                                                                                                                                                                                                                             |           |

| 4.1.3       Host Memory Read       1         4.1.4       Host Memory Write       1         4.1.5       Host Command       1         4.1.6       Interrupts       1         4.2       System Clock       1         4.2.1       Clock Source       1                                                                                                                                                                                                                                                                                              |           |

| 4.1.4       Host Memory Write       1         4.1.5       Host Command       1         4.1.6       Interrupts       1         4.2       System Clock       1         4.2.1       Clock Source       1                                                                                                                                                                                                                                                                                                                                           |           |

| 4.1.5       Host Command       1         4.1.6       Interrupts       1         4.2       System Clock       1         4.2.1       Clock Source       1                                                                                                                                                                                                                                                                                                                                                                                         | 151919    |

| 4.1.6 Interrupts       1         4.2 System Clock       1         4.2.1 Clock Source       1                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1919      |

| 4.2 System Clock       1         4.2.1 Clock Source       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>19</b> |

| 4.2.1 Clock Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 19        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |

| 4.2.2 Phase Locked Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 20        |

| 4.2.3 Clock Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20        |

| 4.2.4 Clock Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20        |

| 4.3 Graphics Engine2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20        |

| 4.3.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20        |

| 4.3.2 ROM and RAM Fonts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 21        |

| 4.4 Parallel RGB Interface 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25        |

| 4.5 Miscellaneous Control2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 27        |

| 4.5.1 Backlight Control Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 27        |

| 4.5.2 DISP Control Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27        |

| 4.5.3 General Purpose IO pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 27        |

| 4.5.4 Pins Drive Current Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 27        |

| 4.6 Audio Engine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 28        |

| 4.6.1 Sound Synthesizer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |

| 4.6.2 | Audio Playback                       | 30 |

|-------|--------------------------------------|----|

| 4.7 T | ouch-Screen Engine                   | 30 |

| 4.7.1 | Resistive Touch Control              | 30 |

| 4.7.2 | Capacitive Touch Control             | 31 |

| 4.7.3 | Compatibility mode                   | 32 |

| 4.7.4 | Extended mode                        | 32 |

| 4.7.5 | Short-circuit protection             | 32 |

| 4.7.6 | Capacitive touch configuration       | 33 |

| 4.7.7 | Touch detection in none-ACTIVE state | 33 |

| 4.8 P | Power Management                     | 33 |

| 4.8.1 | Power supply                         | 33 |

| 4.8.2 | Internal Regulator and POR           | 33 |

| 4.8.3 | Power Modes                          | 34 |

| 4.8.4 | Reset and boot-up sequence           |    |

| 4.8.5 | Pin Status at Different Power States |    |

| 5 Me  | mory Map                             | 38 |

| 5.1 R | Registers                            | 38 |

| 5.2 C | Chip ID                              | 41 |

| 6 Dev | vices Characteristics and Ratings    | 42 |

|       | Absolute Maximum Ratings             |    |

|       | SD and Latch-up Specifications       |    |

|       | OC Characteristics                   |    |

|       |                                      |    |

| _     | AC Characteristics                   |    |

|       | System clock and reset               |    |

| 6.4.2 | SPI interface timing                 |    |

| 6.4.3 | RGB Interface Timing                 |    |

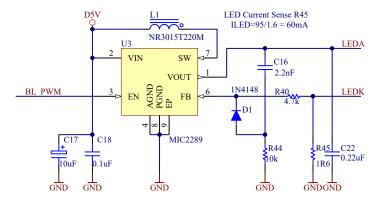

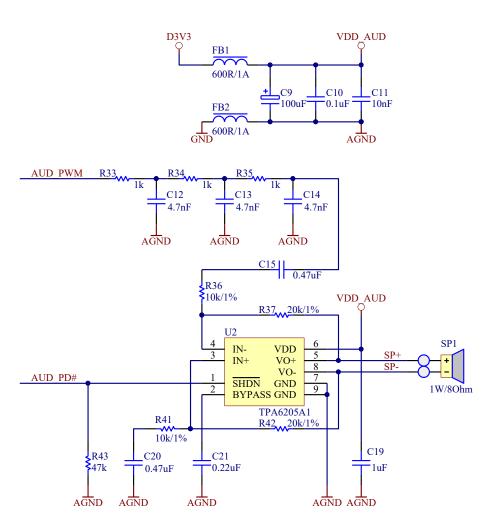

| 7 App | plication Examples                   | 46 |

| 8 Pag | ckage Parameters                     | 48 |

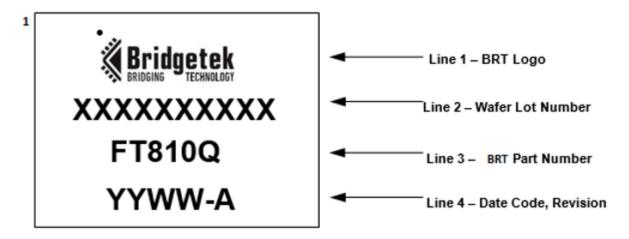

| 8.1 P | Part Markings                        | 48 |

| 8.1.1 | Top side                             | 48 |

| 8.1.2 | Bottom Side                          | 48 |

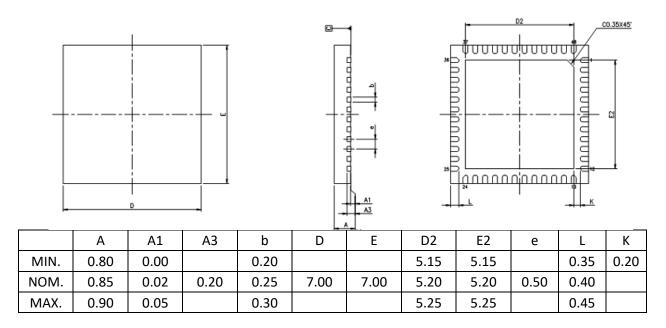

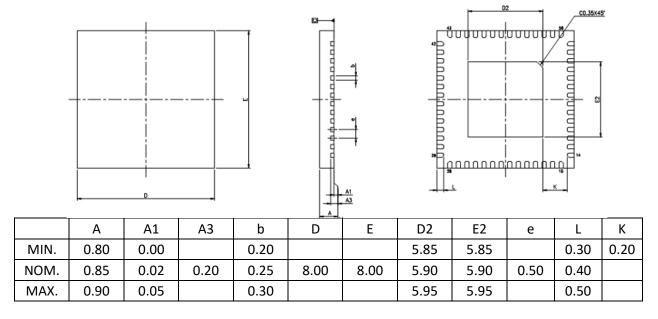

| 8.2 V | QFN-48 Package Dimensions            | 49 |

| 8.3 V | QFN-56 Package Dimensions            | 49 |

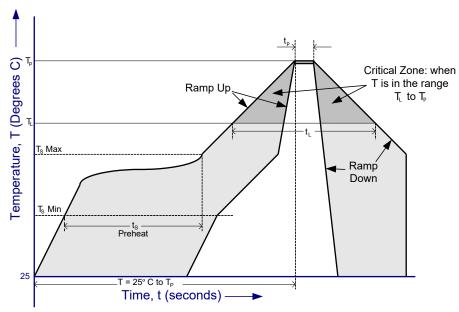

|       | Solder Reflow Profile                |    |

|       | ntact Information                    |    |

|       |                                      |    |

| Appendix A – References                 | 52 |

|-----------------------------------------|----|

| Document References                     | 52 |

| Acronyms and Abbreviations              | 52 |

| Appendix B - List of Figures and Tables | 54 |

| List of Figures                         | 54 |

| List of Tables                          | 54 |

| Appendix C - Revision History           | 56 |

## 3 Device Pin Out and Signal Description

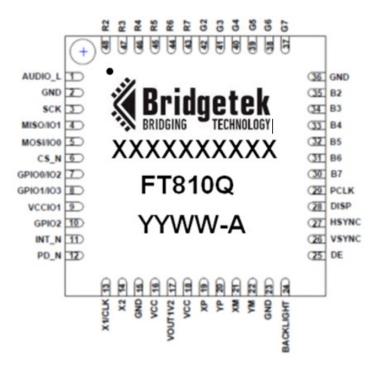

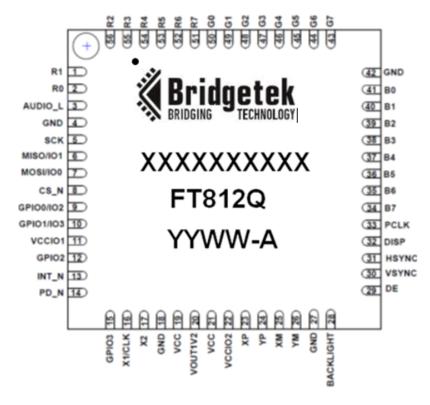

# 3.1 FT810 VQFN-48 Package Pin Out

Figure 3-1 Pin Configuration FT810 VQFN-48 (Top View)

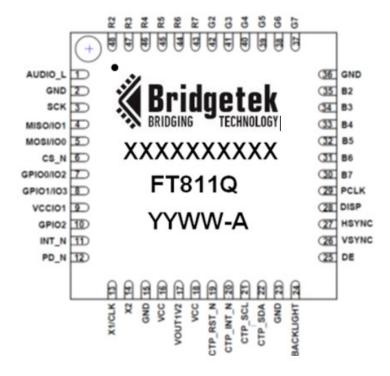

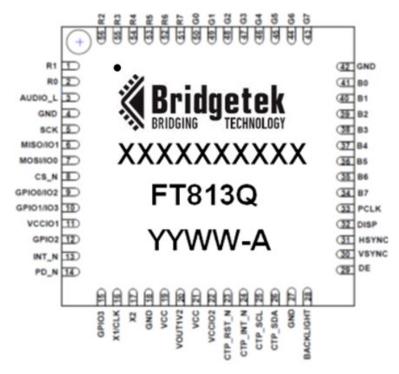

## 3.2 FT811 VQFN-48 Package Pin Out

Figure 3-2 Pin Configuration FT811 VQFN-48 (Top View)

# 3.3 FT812 VQFN-56 Package Pin Out

Figure 3-3 Pin Configuration FT812 VQFN-56 (Top View)

# 3.4 FT813 VQFN-56 Package Pin Out

Figure 3-1 Pin Configuration FT813 VQFN-56 (top view)

# 3.5 Pin Description

| Pin Number |       |       |       |               |      |                                                                                                                                                                                                                                                         |  |  |

|------------|-------|-------|-------|---------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| FT810      | FT811 | FT812 | FT813 | Pin Name Type |      | Description                                                                                                                                                                                                                                             |  |  |

| -          | -     | 1     | 1     | R1            | 0    | Bit 1 of Red RGB signals<br>Powered from pin VCCIO2                                                                                                                                                                                                     |  |  |

| -          | -     | 2     | 2     | R0            | 0    | Bit 0 of Red RGB signals<br>Powered from pin VCCIO2                                                                                                                                                                                                     |  |  |

| 1          | 1     | 3     | 3     | AUDIO_L       | 0    | Audio PWM out Powered from pin VCC                                                                                                                                                                                                                      |  |  |

| 2          | 2     | 4     | 4     | GND           | Р    | Ground                                                                                                                                                                                                                                                  |  |  |

| 3          | 3     | 5     | 5     | SCK           | I    | SPI clock input Powered from pin VCCIO1                                                                                                                                                                                                                 |  |  |

| 4          | 4     | 6     | 6     | MISO/IO1      | I/O  | SPI Single mode: SPI MISO output<br>SPI Dual/Quad mode: SPI data line 1<br>Powered from pin VCCIO1                                                                                                                                                      |  |  |

| 5          | 5     | 7     | 7     | MOSI/IO0      | I/O  | SPI Single mode: SPI MOSI input<br>SPI Dual/Quad mode: SPI data line 0<br>Powered from pin VCCIO1                                                                                                                                                       |  |  |

| 6          | 6     | 8     | 8     | CS_N          | I    | SPI slave select input Powered from pin VCCIO1                                                                                                                                                                                                          |  |  |

| 7          | 7     | 9     | 9     | GPIO0/IO2     | I/O  | SPI Single/Dual mode: General purpose IO 0<br>SPI Quad mode: SPI data line 2<br>Powered from pin VCCIO1                                                                                                                                                 |  |  |

| 8          | 8     | 10    | 10    | GPIO1/IO3     | I/O  | SPI Single/Dual mode: General purpose IO 1<br>SPI Quad mode: SPI data line 3<br>Powered from pin VCCIO1                                                                                                                                                 |  |  |

| 9          | 9     | 11    | 11    | VCCIO1        | Р    | I/O power supply for host interface pins. Support 1.8V, 2.5V or 3.3V.                                                                                                                                                                                   |  |  |

| 10         | 10    | 12    | 12    | GPIO2         | I/O  | General purpose IO 2<br>Powered from pin VCCIO1                                                                                                                                                                                                         |  |  |

| 11         | 11    | 13    | 13    | INT_N         | OD/O | Interrupt to host, open drain output(default) or push-<br>pull output, active low                                                                                                                                                                       |  |  |

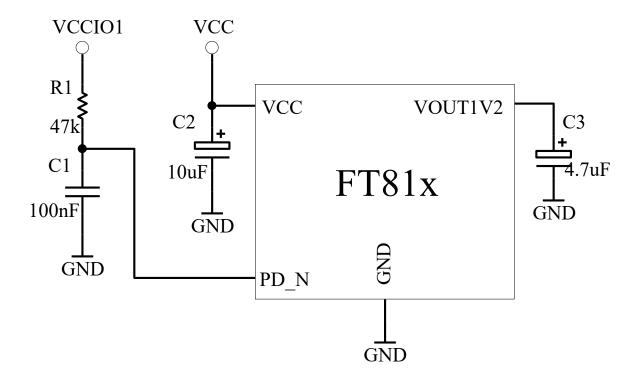

| 12         | 12    | 14    | 14    | PD_N          | I    | Chip power down mode control input, active low. Connect to MCU GPIO for power management or hardware reset function or pulled up to VCCIO1 through $47k\Omega$ resistor and $100nF$ to ground. Powered from pin VCCIO1                                  |  |  |

| -          | -     | 15    | 15    | GPIO3         | I/O  | General purpose IO 3 Powered from pin VCCIO1                                                                                                                                                                                                            |  |  |

| 13         | 13    | 16    | 16    | X1/CLK        | I    | Crystal oscillator or clock input; Connect to GND if not used. 3.3V peak input allowed. Powered from pin VCC.                                                                                                                                           |  |  |

| 14         | 14    | 17    | 17    | X2            | 0    | Crystal oscillator output; leave open if not used. Powered from pin VCC.                                                                                                                                                                                |  |  |

| 15         | 15    | 18    | 18    | GND           | Р    | Ground                                                                                                                                                                                                                                                  |  |  |

| 16         | 16    | 19    | 19    | VCC           | Р    | 3.3V power supply input.                                                                                                                                                                                                                                |  |  |

| 17         | 17    | 20    | 20    | VOUT1V2       | 0    | 1.2V regulator output pin. Connect a 4.7uF decoupling capacitor to GND.                                                                                                                                                                                 |  |  |

|            |       | 21    | 21    | VCC           | Р    | 3.3V power supply input.                                                                                                                                                                                                                                |  |  |

| 18         | 18    | 22    | 22    | VCCIO2        | Р    | I/O power supply for RGB and touch pins. For QFN-48 package, VCCIO2 is bonded together with VCC pin; For QFN-56 package, VCCIO2 is separate from VCC pin. VCCIO2 supports 1.8V, 2.5V or 3.3V. VCCIO2 can be connected to different voltage with VCCIO1. |  |  |

| 19         |       | 23    |       | XP            | AI/O | Connect to X right electrode of 4-wire resistive touch-<br>screen panel.<br>Powered from pin VCCIO2.                                                                                                                                                    |  |  |

| 20         |       | 24    |       | YP            | AI/O | Connect to Y top electrode of 4-wire resistive touch-screen panel.                                                                                                                                                                                      |  |  |

Document No.: BRT\_000002 Clearance No.: BRT#004

| Pin Number |       |       |       |           |                                                                                                |                                                                                                |

|------------|-------|-------|-------|-----------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| FT810      | FT811 | FT812 | FT813 | Pin Name  | Туре                                                                                           | Description                                                                                    |

|            |       |       |       |           |                                                                                                | Powered from pin VCCIO2.                                                                       |

| 21         |       | 25    |       | XM        | AI/O Connect to X left electrode of 4-wire resistive to screen panel. Powered from pin VCCIO2. |                                                                                                |

| 22         |       | 26    |       | YM        | AI/O                                                                                           | Connect to Y bottom electrode of 4-wire resistive touch-screen panel. Powered from pin VCCIO2. |

| -          | 19    | -     | 23    | CTP_RST_N | 0                                                                                              | Connect to reset pin of the CTPM. Powered from pin VCCIO2.                                     |

| -          | 20    | -     | 24    | CTP_INT_N | I                                                                                              | Connect to interrupt pin of the CTPM. Powered from pin VCCIO2.                                 |

| -          | 21    | -     | 25    | CTP_SCL   | I/OD                                                                                           | Connect to I2C SCL pin of the CTPM. Powered from pin VCCIO2.                                   |

| -          | 22    | 1     | 26    | CTP_SDA   | I/OD                                                                                           | Connect to I2C SDA pin of the CTPM. Powered from pin VCCIO2.                                   |

| 23         | 23    | 27    | 27    | GND       | Р                                                                                              | Ground                                                                                         |

| 24         | 24    | 28    | 28    | BACKLIGHT | 0                                                                                              | LED Backlight brightness PWM control signal. Powered from pin VCCIO2.                          |

| 25         | 25    | 29    | 29    | DE        | 0                                                                                              | LCD Data Enable. Powered from pin VCCIO2.                                                      |

| 26         | 26    | 30    | 30    | VSYNC     | 0                                                                                              | LCD Vertical Sync. Powered from pin VCCIO2.                                                    |

| 27         | 27    | 31    | 31    | HSYNC     | 0                                                                                              | LCD Horizontal Sync. Powered from pin VCCIO2.                                                  |

| 28         | 28    | 32    | 32    | DISP      | 0                                                                                              | LCD Display Enable. Powered from pin VCCIO2.                                                   |

| 29         | 29    | 33    | 33    | PCLK      | 0                                                                                              | LCD Pixel Clock. Powered from pin VCCIO2.                                                      |

| 30         | 30    | 34    | 34    | В7        | 0                                                                                              | Bit 7 of Blue RGB signals. Powered from pin VCCIO2.                                            |

| 31         | 31    | 35    | 35    | B6        | 0                                                                                              | Bit 6 of Blue RGB signals. Powered from pin VCCIO2.                                            |

| 32         | 32    | 36    | 36    | B5        | 0                                                                                              | Bit 5 of Blue RGB signals. Powered from pin VCCIO2.                                            |

| 33         | 33    | 37    | 37    | B4        | 0                                                                                              | Bit 4 of Blue RGB signals. Powered from pin VCCIO2.                                            |

| 34         | 34    | 38    | 38    | B3        | 0                                                                                              | Bit 3 of Blue RGB signals. Powered from pin VCCIO2.                                            |

| 35         | 35    | 39    | 39    | B2        | 0                                                                                              | Bit 2 of Blue RGB signals. Powered from pin VCCIO2.                                            |

| -          | -     | 40    | 40    | B1        | 0                                                                                              | Bit 1 of Blue RGB signals. Powered from pin VCCIO2.                                            |

| -          | -     | 41    | 41    | В0        | 0                                                                                              | Bit 0 of Blue RGB signals. Powered from pin VCCIO2.                                            |

| 36         | 36    | 42    | 42    | GND       | Р                                                                                              | Ground                                                                                         |

| 37         | 37    | 43    | 43    | G7        | 0                                                                                              | Bit 7 of Green RGB signals. Powered from pin VCCIO2.                                           |

| 38         | 38    | 44    | 44    | G6        | 0                                                                                              | Bit 6 of Green RGB signals. Powered from pin VCCIO2.                                           |

| 39         | 39    | 45    | 45    | G5        | 0                                                                                              | Bit 5 of Green RGB signals. Powered from pin VCCIO2.                                           |

| 40         | 40    | 46    | 46    | G4        | 0                                                                                              | Bit 4 of Green RGB signals. Powered from pin VCCIO2.                                           |

| 41         | 41    | 47    | 47    | G3        | 0                                                                                              | Bit 3 of Green RGB signals. Powered from pin VCCIO2.                                           |

| 42         | 42    | 48    | 48    | G2        | 0                                                                                              | Bit 2 of Green RGB signals. Powered from pin VCCIO2.                                           |

| -          | -     | 49    | 49    | G1        | 0                                                                                              | Bit 1 of Green RGB signals. Powered from pin VCCIO2.                                           |

| -          | -     | 50    | 50    | G0        | 0                                                                                              | Bit 0 of Green RGB signals. Powered from pin VCCIO2.                                           |

| 43         | 43    | 51    | 51    | R7        | 0                                                                                              | Bit 7 of Red RGB signals.<br>Powered from pin VCCIO2.                                          |

Document No.: BRT\_000002 Clearance No.: BRT#004

|       | Pin N | umber |       | Pin Name Type |   | Description                                        |  |  |

|-------|-------|-------|-------|---------------|---|----------------------------------------------------|--|--|

| FT810 | FT811 | FT812 | FT813 |               |   | Description                                        |  |  |

| 44    | 44    | 52    | 52    | R6            | 0 | Bit 6 of Red RGB signals. Powered from pin VCCIO2. |  |  |

| 45    | 45    | 53    | 53    | R5            | 0 | Bit 5 of Red RGB signals. Powered from pin VCCIO2. |  |  |

| 46    | 46    | 54    | 54    | R4            | 0 | Bit 4 of Red RGB signals. Powered from pin VCCIO2. |  |  |

| 47    | 47    | 55    | 55    | R3            | 0 | Bit 3 of Red RGB signals. Powered from pin VCCIO2. |  |  |

| 48    | 48    | 56    | 56    | R2            | 0 | Bit 2 of Red RGB signals. Powered from pin VCCIO2. |  |  |

| EP    | EP    | EP    | EP    | GND           | Р | Ground. Exposed thermal pad.                       |  |  |

Table 3-1 FT81x pin description

#### Note:

P : Power or ground

I : InputO : Output

OD : Open drain output

I/O : Bi-direction Input and Output AI/O: Analog Input and Output

Document No.: BRT\_000002 Clearance No.: BRT#004

# **4 Function Description**

The FT81x is a single chip, embedded video controller with the following function blocks:

- · Quad SPI Host Interface

- System Clock

- Graphics Engine

- Parallel RGB video interface

- Audio Engine

- Touch-screen support and interface

- Power Management

The functions for each block are briefly described in the following subsections.

## 4.1 Quad SPI Host Interface

The FT81x uses a quad serial parallel interface (QSPI) to communicate with host microcontrollers and microprocessors.

#### 4.1.1 QSPI Interface

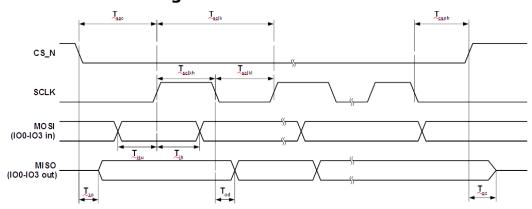

The QSPI slave interface operates up to 30MHz. Only SPI mode 0 is supported. Refer to section 6.4.2 for detailed timing specification. The QSPI can be configured as a SPI slave in SINGLE, DUAL or QUAD channel modes.

By default, the SPI slave operates in the SINGLE channel mode with MOSI as input from the master and MISO as output to the master. DUAL and QUAD channel modes can be configured through the SPI slave itself. To change the channel modes, write to register REG\_SPI\_WIDTH. The table below depicts the setting.

| REG_SPI_WIDTH[1:0] | Channel Mode          | Data pins          | Max bus speed |

|--------------------|-----------------------|--------------------|---------------|

| 00                 | SINGLE – default mode | MISO, MOSI         | 30 MHz        |

| 01                 | DUAL                  | IO0, IO1           | 30 MHz        |

| 10                 | QUAD                  | IO0, IO1, IO2, IO3 | 25 MHz        |

| 11                 | Reserved              | -                  | -             |

Table 4-1 QSPI channel selection

With DUAL/QUAD channel modes, the SPI data ports are now unidirectional. In these modes, each SPI transaction (signified by CS N going active low) will begin with the data ports set as inputs.

Hence, for writing to the FT81x, the protocol will operate as in FT800, with "WR-Command/Addr2, Addr1, Addr0, DataX, DataY, DataZ ..." The write operation is considered complete when CS\_N goes inactive high.

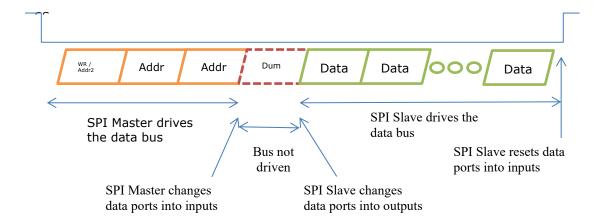

For reading from the FT81x, the protocol will still operate as in FT800, with "RD-Command/Addr2, Addr1, Addr0, Dummy-Byte, DataX, DataY, DataZ". However, as the data ports are now unidirectional, a change of port direction will occur before DataX is clocked out of the FT81x. Therefore, it is important that the firmware controlling the SPI master changes the SPI master data port direction to "input" after transmitting Addr0. The FT81x will not change the port direction till it starts to clock out DataX. Hence, the Dummy-Byte cycles will be used as a change-over period when neither the SPI master nor slave will be driving the bus; the data paths thus must have pull-ups/pull-downs. The SPI slave from the FT81x will reset all its data ports' direction to input once CS\_N goes inactive high (i.e. at the end of the current SPI master transaction).

The diagram depicts the behaviour of both the SPI master and slave in the master read case.

Figure 4-1 SPI master and slave in the master read case

In the DUAL channel mode, MISO (MSB) and MOSI are used while in the QUAD channel mode. IO3 (MSB), IO2, MISO and MOSI are used.

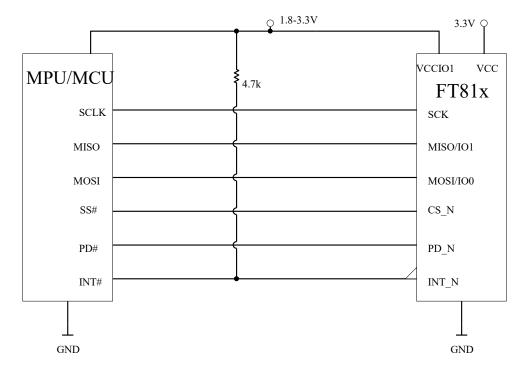

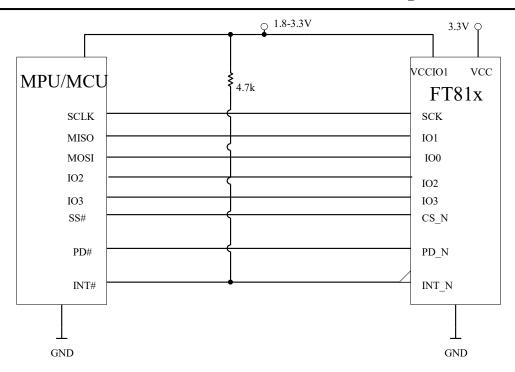

Figure 4-2 illustrates a direct connection to a 1.8-3.3V IO MPU/MCU with single or dual SPI interface.

Figure 4-3 illustrates a direct connection to a 1.8-3.3V IO MPU/MCU with Quad SPI interface.

Figure 4-2 Single/Dual SPI Interface connection

Figure 4-3 Quad SPI Interface connection

#### 4.1.2 Serial Data Protocol

The FT81x appears to the host MPU/MCU as a memory-mapped SPI device. The host communicates with the FT81x using reads and writes to a large (4 megabyte) address space. Within this address space are dedicated areas for graphics, audio and touch control. Refer to section 5 for the detailed memory map.

The host reads and writes the FT81x address space using SPI transactions. These transactions are memory read, memory write and command write. Serial data is sent by the most significant bit first. Each transaction starts with CS\_N goes low and ends when CS\_N goes high. There's no limit on data length within one transaction, as long as the memory address is continuous.

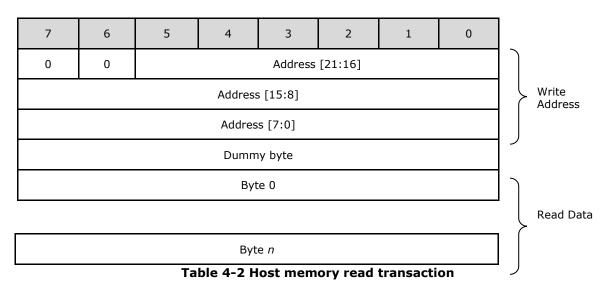

#### 4.1.3 Host Memory Read

For SPI memory read transactions, the host sends two zero bits, followed by the 22-bit address. This is followed by a dummy byte. After the dummy byte, the FT81x responds to each host byte with read data bytes.

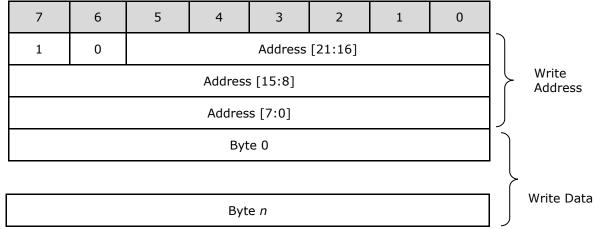

#### 4.1.4 Host Memory Write

For SPI memory write transactions, the host sends a 1' bit and 0' bit, followed by the 22-bit address. This is followed by the write data.

Table 4-3 Host memory write transaction

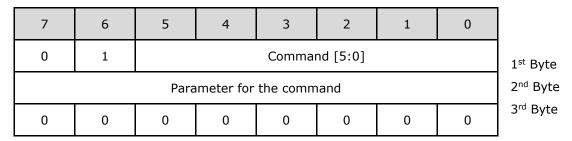

#### 4.1.5 Host Command

When sending a command, the host transmits a 3 byte command. **Error! Reference source not found.** Table 4-5 lists all the host command functions.

For SPI command transactions, the host sends a '0' bit and '1' bit, followed by the 6-bit command code. The  $2^{nd}$  byte can be either 00h, or the parameter of that command. The  $3^{rd}$  byte is fixed at 00h.

All SPI commands except the system reset can only be executed when the SPI is in the Single channel mode. They will be ignored when the SPI is in either Dual or Quad channel mode.

Some commands are used to configure the device and these configurations will be reset upon receiving the SPI PWRDOWN command, except those that configure the pin state during power down. These commands will be sticky unless reconfigured or power-on-reset (POR) occurs.

**Table 4-4 Host command transaction**

| 1st Byte    | 2nd byte  | 3rd byte  | Command        | Description                                                                                                                    |  |  |  |  |

|-------------|-----------|-----------|----------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Power Modes |           |           |                |                                                                                                                                |  |  |  |  |

| 00000000ь   | 00000000ь | 00000000b | 00h<br>ACTIVE  | Switch from Standby/Sleep/PWRDOWN modes to active mode. Dummy memory read from address 0(read twice) generates ACTIVE command. |  |  |  |  |

| 01000001b   | 00000000ь | 00000000b | 41h<br>STANDBY | Put FT81x core to standby mode. Clock gate off, PLL and Oscillator remain on (default). ACTIVE command to wake up.             |  |  |  |  |

| 01000010b   | 0000000b  | 0000000b  | 42h            | Put FT81x core to sleep mode. Clock                                                                                            |  |  |  |  |

Document No.: BRT\_000002 Clearance No.: BRT#004

| 1st Byte  | 2nd byte  | 3rd byte  | Command       | Description                                                                           |  |  |

|-----------|-----------|-----------|---------------|---------------------------------------------------------------------------------------|--|--|

| 1st byte  | Zilu byte | Sid byte  | SLEEP         | gate off, PLL and Oscillator off. ACTIVE                                              |  |  |

|           |           |           | SLEEP         | command to wake up.                                                                   |  |  |

|           |           |           |               | Switch off 1.2V core voltage to the                                                   |  |  |

| 01000011b | 00000000ь | 00000000b | 43h/50h       | digital core circuits. Clock, PLL and                                                 |  |  |

| 01010000b | 00000000  | 00000000  | PWRDOWN       | Oscillator off. SPI is alive. ACTIVE                                                  |  |  |

|           |           |           |               | command to wake up.  Select power down individual ROMs;                               |  |  |

|           |           |           |               | Byte2 determines which ROM to power                                                   |  |  |

|           |           |           |               | down or up. A 1 on a bit power down the                                               |  |  |

|           |           |           |               | corresponding block; a 0 on a bit power                                               |  |  |

|           |           |           |               | up the corresponding block. As these are                                              |  |  |

|           |           |           |               | not readable, the host must remember the setting on its own.                          |  |  |

|           |           |           |               | Byte2[7] ROM_MAIN                                                                     |  |  |

|           |           |           |               |                                                                                       |  |  |

| 01000100b | xx        | 0000000b  | 49h           | Byte2[6] ROM_RCOSATAN                                                                 |  |  |

|           |           |           | PD_ROMS       |                                                                                       |  |  |

|           |           |           |               | Byte2[5] ROM_SAMPLE                                                                   |  |  |

|           |           |           |               | Byte2[4] ROM_JABOOT                                                                   |  |  |

|           |           |           |               | bytez[4]   KON_SABOOT                                                                 |  |  |

|           |           |           |               | Byte2[3] ROM_J1BOOT                                                                   |  |  |

|           |           |           |               |                                                                                       |  |  |

|           |           |           |               | Byte2[2- reserved                                                                     |  |  |

|           |           |           | 0111 D        | [ 0]                                                                                  |  |  |

|           |           |           | Clock and Res | -                                                                                     |  |  |

|           |           |           |               | Select PLL input from external crystal oscillator or external input clock. No         |  |  |

| 01000100b | 00000000ь | 0000000b  | 44h           | effect if external clock is already                                                   |  |  |

|           |           |           | CLKEXT        | selected, otherwise a system reset will                                               |  |  |

|           |           |           |               | be generated                                                                          |  |  |

|           |           |           | 48h           | Select PLL input from internal relaxation oscillator (default). No effect if internal |  |  |

| 01001000b | 0000000b  | 0000000b  | CLKINT        | clock is already selected, otherwise a                                                |  |  |

|           |           |           |               | system reset will be generated                                                        |  |  |

|           |           |           |               | This command will only be effective                                                   |  |  |

|           |           |           |               | when the PLL is stopped (SLEEP mode). For compatibility to FT800/FT801, set           |  |  |

|           |           |           |               | Byte2 to 0x00. This will set the PLL clock                                            |  |  |

|           |           |           |               | back to default (60 MHz).                                                             |  |  |

|           |           |           |               | Byte2 sets the clock frequency                                                        |  |  |

|           |           |           |               | [5:0]                                                                                 |  |  |

|           |           |           |               | 0 Set to default clock speed                                                          |  |  |

|           |           |           |               | Set to default clock speed                                                            |  |  |

|           |           |           |               | 1 Reserved                                                                            |  |  |

| 01100001b | xx        | 00000000b | 61h/62h       |                                                                                       |  |  |

| 01100010b |           |           | CLKSEL        | 2 to 5 2 to 5 times the osc                                                           |  |  |

|           |           |           |               | frequency (i.e. 24 to 60MHz                                                           |  |  |

|           |           |           |               | with 12MHz oscillator)                                                                |  |  |

|           |           |           |               | Byte2 sets the PLL range                                                              |  |  |

|           |           |           |               | [7:6]                                                                                 |  |  |

|           |           |           |               |                                                                                       |  |  |

|           |           |           |               | 0 When Byte2[5:0] = 0, 2, 3                                                           |  |  |

|           |           |           |               |                                                                                       |  |  |

|           |           |           |               | 1 When Byte2[5:0] = 4, 5                                                              |  |  |

|           |           |           |               |                                                                                       |  |  |

Document No.: BRT\_000002 Clearance No.: BRT#004

| 1st Byte  | 2nd byte  | 3rd byte | Command         |                                                                                                                                                                                                        | Description                                                                                         |                                                                                                                                                                                                                                           |  |

|-----------|-----------|----------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 13t Dyte  | Zila byte | Sid Byte | Communa         | Sand rese                                                                                                                                                                                              |                                                                                                     |                                                                                                                                                                                                                                           |  |

|           |           |          | 68h             | Send reset pulse to FT81x core. The behaviour is the same as POR except                                                                                                                                |                                                                                                     |                                                                                                                                                                                                                                           |  |

| 01101000b | 0000000b  | 0000000b | RST_PULSE       |                                                                                                                                                                                                        | ngs done through                                                                                    |                                                                                                                                                                                                                                           |  |

|           |           |          |                 |                                                                                                                                                                                                        | s will not be affe                                                                                  |                                                                                                                                                                                                                                           |  |

|           |           |          | Configuration   | 1                                                                                                                                                                                                      |                                                                                                     |                                                                                                                                                                                                                                           |  |

| 01110000b | XX        | 0000000b | 70h<br>PINDRIVE | This will various compatibi are from supports SPI comm When PIN command strength correspon exist. If t setting is When PIN command correspon register b Byte2 de setting an Byte2[1:0]  Oh  1h  2h  3h | IDRIVE for a ping is updated, it work with the ding setting its.  Stermines which is to be updated. | FT800/FT801 those settings gisters. FT81x re strength via  In from the SPI red, the drive mined by its ter bits, if they red, a hard coded  In from the SPI vill override the in the GPIO red pin and the the drive  The drive  The drive |  |

| 1st Byte  | 2nd byte | 3rd byte  | Command                 |                                                                                                                                                                   | Description                                                                                                                                                                                       |

|-----------|----------|-----------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -         | -        | -         |                         | 0Bh                                                                                                                                                               | PCLK                                                                                                                                                                                              |

|           |          |           |                         | 0Ch                                                                                                                                                               | BACKLIGHT                                                                                                                                                                                         |

|           |          |           |                         | OCII                                                                                                                                                              | DACKLIGITI                                                                                                                                                                                        |

|           |          |           |                         | 0Dh                                                                                                                                                               | R[7:0], G[7:0], B[7:0]                                                                                                                                                                            |

|           |          |           |                         | 0Eh                                                                                                                                                               | AUDIO_L                                                                                                                                                                                           |

|           |          |           |                         | 0Fh                                                                                                                                                               | INT_N                                                                                                                                                                                             |

|           |          |           |                         | 10h                                                                                                                                                               | CTP_RST_N                                                                                                                                                                                         |

|           |          |           |                         | 11h                                                                                                                                                               | CTP_SCL                                                                                                                                                                                           |

|           |          |           |                         | 12h                                                                                                                                                               | CTP_SDA                                                                                                                                                                                           |

|           |          |           |                         | 13h                                                                                                                                                               | SPI MISO/MOSI/IO2/IO3                                                                                                                                                                             |

|           |          |           |                         | Others                                                                                                                                                            | Reserved                                                                                                                                                                                          |

|           |          |           |                         | IO2 and (<br>is set in<br>inherit the<br>13h; othe<br>inherit th                                                                                                  | O0 shares the same pin as SPI GPIO1 with SPI IO3. When SPI Quad mode, IO2 and IO3 will e drive strength set in GROUP erwise GPIO0 and GPIO1 will e drive strength from GROUP of the respectively. |

| 01110001b | xx       | 00000000Ь | 71h<br>PIN_PD_STA<br>TE | in/out pin: These se during po normal op configurat other cond default va Only POR Byte2 de setting are Byte2[1:0 Byte2 [1  Oh  1h  2h  3h  Byte2[7:2 group to se | Float  Pull-Down  Pull-Up  Reserved  determine which pin/pin set. fer to the table in command                                                                                                     |

**Table 4-5 Host command list**

$\underline{\textbf{Note:}}$  Any command code not specified is reserved and should not be used by the software

#### 4.1.6 Interrupts

The interrupt output pin is enabled by REG\_INT\_EN. When REG\_INT\_EN is 0, INT\_N is tri-state (pulled to high by external pull-up resistor). When REG\_INT\_EN is 1, INT\_N is driven low when any of the interrupt flags in REG\_INT\_FLAGS are high, after masking with REG\_INT\_MASK. Writing a `1' in any bit of REG\_INT\_MASK will enable the corresponding interrupt. Each bit in REG\_INT\_FLAGS is set by a corresponding interrupt source. REG\_INT\_FLAGS is readable by the host at any time and clears when read.

The INT\_N pin is open-drain (OD) output by default. It can be configured to push-pull output by register REG\_GPIOX.

| Bit               | 7                                  | 6                             | 5                  | 4                          |

|-------------------|------------------------------------|-------------------------------|--------------------|----------------------------|

| Interrupt Sources | CONVCOMPLETE                       | CMDFLAG                       | CMDEMPTY           | PLAYBACK                   |

| Conditions        | Touch-screen conversions completed | Command FIFO flag             | Command FIFO empty | Audio playback<br>ended    |

| Bit               | 3                                  | 2                             | 1                  | 0                          |

| Interrupt Sources | SOUND                              | TAG                           | TOUCH              | SWAP                       |

| Conditions        | Sound effect ended                 | Touch-screen tag value change | touch detected     | Display list swap occurred |

Table 4-6 Interrupt Flags bit assignment

#### 4.2 System Clock

#### 4.2.1 Clock Source

The FT81x can be configured to use any of the three clock sources for system clock:

- Internal relaxation oscillator clock (default)

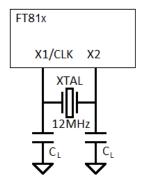

- External 12MHz crystal

- External 12MHz square wave clock

Figure 4-4, Figure 4-5 and Figure 4-6 show the pin connections for these clock options.

Figure 4-4 Internal relaxation oscillator connection

Figure 4-5 Crystal oscillator connection

Figure 4-6 External clock input

#### 4.2.2 Phase Locked Loop

The internal PLL takes an input clock from the oscillator, and generates clocks to all internal circuits, including the graphics engine, audio engine and touch engine.

#### 4.2.3 Clock Enable

At power-on the FT81x enters sleep mode. The internal relaxation oscillator is selected for the PLL clock source. The system clock will be enabled when the following step is executed:

Host sends an "ACTIVE" command

If the application chooses to use the external clock source (12MHz crystal or clock), the following steps shall be executed:

- Host sends a "CLKEXT" command

- Host sends an "ACTIVE" command

#### 4.2.4 Clock Frequency

By default, the system clock is 60MHz when the input clock is 12MHz. The host is allowed to switch the system clock to other frequencies (48MHz, 36MHz, and 24MHz) by the host command "CLKSEL". The clock switching command shall be sent in SLEEP mode only.

When using the internal relaxation oscillator, its clock frequency is trimmed to be 12MHz at factory. Software is allowed to change the frequency to a lower value by programming the register REG\_TRIM. Note that software shall not change the internal oscillator frequency to be higher than 12MHz.

# 4.3 Graphics Engine

#### 4.3.1 Introduction

The graphics engine executes the display list once for every horizontal line. It executes the primitive objects in the display list and constructs the display line buffer. The horizontal pixel content in the line buffer is updated if the object is visible at the horizontal line.

Main features of the graphics engine are:

- The primitive objects supported by the graphics processor are: lines, points, rectangles, bitmaps (comprehensive set of formats), text display, plotting bar graph, edge strips, and line strips, etc.

- Operations such as stencil test, alpha blending and masking are useful for creating a rich set of effects such as shadows, transitions, reveals, fades and wipes.

- Anti-aliasing of the primitive objects (except bitmaps) gives a smoothing effect to the viewer.

- Bitmap transformations enable operations such as translate, scale and rotate.

- Display pixels are plotted with 1/16<sup>th</sup> pixel precision.

- Four levels of graphics states

#### Tag buffer detection

The graphics engine also supports customized built-in widgets and functionalities such as jpeg decode, screen saver, calibration etc. The graphics engine interprets commands from the MPU host via a 4 Kbyte FIFO in the FT81x memory at RAM\_CMD. The MPU/MCU writes commands into the FIFO, and the graphics engine reads and executes the commands. The MPU/MCU updates the register REG\_CMD\_WRITE to indicate that there are new commands in the FIFO, and the graphics engine updates REG\_CMD\_READ after commands have been executed.

#### Main features supported are:

- Drawing of widgets such as buttons, clock, keys, gauges, text displays, progress bars, sliders, toggle switches, dials, gradients, etc.

- JPEG and motion-JPEG decode

- Inflate functionality (zlib inflate is supported)

- Timed interrupt (generate an interrupt to the host processor after a specified number of milliseconds)

- In-built animated functionalities such as displaying logo, calibration, spinner, screen saver and sketch

- Snapshot feature to capture the current graphics display

For a complete list of graphics engine display commands and widgets refer to FT81x Series Programmer Guide, Chapter 4.

#### 4.3.2 ROM and RAM Fonts