# BT820 Framebuffer based Embedded Video Engine

# **Datasheet**

The BT820 is the 5<sup>th</sup> Generation Embedded Video Engine (EVE), an easy-to-use family of graphics controller targeted at embedded applications to generate advanced high-quality Human Machine Interfaces (HMIs). It has the following features:

- Graphics, video input, audio output, and touch control interface

- · Unified memory model

- 24-bit RGB framebuffer up to 2048 x 2048 pixels

- Render engine to accelerate image processing tasks

- Render-to-bitmap capability

- Hardware INFLATE engine

- Hardware PNG decompression engine

- Supports 24-bit RGB and 32-bit RGBA

- Supports full-speed paletted bitmaps, and 32-bit RGBA palettes

- Supports playback of motion-JPEG encoded AVI videos

- Supports YCbCr frame buffer format

- Real-time processing for input video stream

- Supports 2 channels, each with 4 data lanes, LVDS transmit interface up to 1920x1200 pixel resolution

- Supports 2 channels, each with 4 data lanes, LVDS receive interface up to 1920x1200 pixel resolution

- Supports external DDR3 / DDR3L / LPDDR2 DRAM up to 4Gbit to speed up video processing

- Supports QSPI host interface in Single, Dual, or Quad mode up to 60MHz

- Supports QSPI NOR / NAND flash memory devices

- Supports SD Card Interface

- Supports an I2C master interface to external touch screen controller device.

- Supports auto discovery feature to discover attached touch controller

- Hardware touch engine to recognize touch tags and track touch movements with up to 5 touch point detection.

- Supports stereo audio channel outputs

- Supports I2S output interface

- Built-in sound synthesizer

- Integrated 32-bit watchdog timer

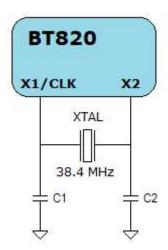

- Integrated 38.4MHz crystal oscillator with PLL providing a programmable system clock up to 72MHz

- Supports various low power modes

- Supports multiple I/O voltage of 1.8V, 2.5V or 3.3V

- Internal voltage regulator supplies 1.0V to the digital core

- Built-in Power-on-reset circuit

- -40°C to 85°C extended operating temperature range

- Available in a compact Pb-free, 329 Ball package, RoHS compliant

Neither the whole nor any part of the information contained in, or the product described in this manual, may be adapted, or reproduced in any material or electronic form without the prior written consent of the copyright holder. This product and its documentation are supplied on an as-is basis and no warranty as to their suitability for any particular purpose is either made or implied. Bridgetek Pte Ltd will not accept any claim for damages howsoever arising as a result of use or failure of this product. Your statutory rights are not affected. This product or any variant of it is not intended for use in any medical appliance, device, or system in which the failure of the product might reasonably be expected to result in personal injury. This document provides preliminary information that may be subject to change without notice. No freedom to use patents or other intellectual property rights is implied by the publication of this document. Bridgetek Pte Ltd, 1 Tai Seng Avenue, Tower A, #03-05, Singapore 536464. Singapore Registered Company Number: 201542387H

# 1 Typical Applications

- Point of Sales Machines

- Multi-function Printers

- Instrumentation

- Home Security Systems

- Graphic touch pad remote, dial pad

- Tele / Video Conference Systems

- Phones and Switchboards

- Medical Appliances

- Blood Pressure displays

- Heart monitors

- Glucose level displays

- Automotive

- Digital Photo Frame

- Breathalyzers

- Gas chromatographs

- Power meter

- Home appliance devices

- Set-top box

- Thermostats

- Sprinkler system displays

- GPS / Satnav

- Vending Machine Control Panels

- Elevator Controls

- Interactive Photo Booth

- Smart Door Bell System

- .....and many more

#### 1.1 Part Numbers

| Part Number | Description                                                                                                                | Package                        |

|-------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| BT820B      | EVE5, 5 <sup>th</sup> Generation Embedded Video Engine with DDR DRAM frame-buffer and dual-channel LVDS inputs and outputs | 329 Ball LFBGA,<br>17x17x1.5mm |

Table 1 - EVE5 Embedded Video Engine Part Numbers

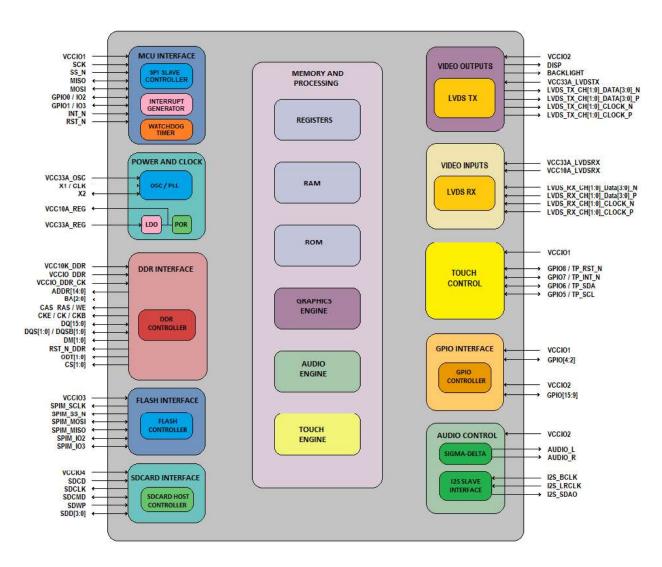

# 2 Block Diagram

Figure 1 - BT820 Block Diagram

Please refer to Section 4 for descriptions of each function.

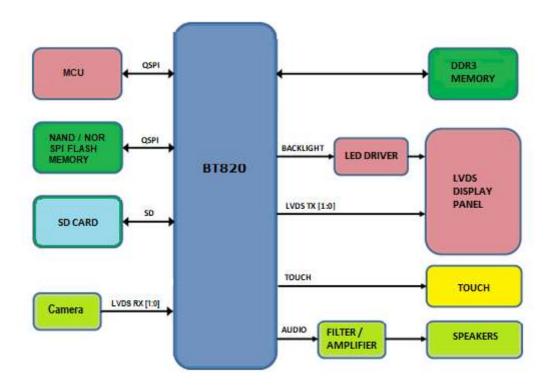

Figure 2 - BT820 System Design Diagram

BT820 with EVE (Embedded Video Engine) technology simplifies the system architecture for advanced human machine interfaces (HMIs) by providing support for display, audio, and touch as well as an object-oriented architecture approach that extends from display creation to the rendering of the graphics.

# **Table of Contents**

| 1 Tyբ          | pical Applications                  | 2  |

|----------------|-------------------------------------|----|

| 1.1 Pa         | art Numbers                         | 2  |

| 2 Blo          | ock Diagram                         | 3  |

|                | vice Pin Out and Signal Description |    |

|                | T820B Package Pin Out               |    |

|                | n Description                       |    |

|                | nctional Description                |    |

|                |                                     |    |

|                | raphics Engine                      |    |

| 4.1.1          | Introduction                        |    |

| 4.1.2<br>4.1.3 | Hardware INFLATE Engine             |    |

| 4.1.3          | YCbCr Format                        |    |

| 4.1.4          | Render Engine                       |    |

| 4.1.6          | ASTC                                |    |

| 4.1.7          | ROM and RAM Fonts                   |    |

|                | ideo Outputs                        |    |

| 4.2.1          | ExtSync                             |    |

| 4.2.2          | LVDS Transmit Interface             |    |

|                | /DS Receive Interface               |    |

|                | DR DRAM Interface                   |    |

|                |                                     |    |

| _              | uad SPI Host Interface              |    |

|                | QSPI Host Interface Protocol        |    |

| 4.5.2          | Serial Data Protocol                |    |

| 4.5.3          | Host Memory Read                    |    |

| 4.5.4          | Host Memory Write                   |    |

|                | ost Commands                        |    |

| _              | uad SPI Flash Interface             |    |

| 4.8 SI         | D Card Host Controller              | 28 |

| 4.9 To         | ouch Engine and Interface           | 28 |

| 4.10 A         | udio Engine                         | 29 |

| 4.10.1         | Sound Synthesizer                   | 29 |

| 4.10.2         | Audio Playback                      | 31 |

| 4.11 Au | ıdio Outputs / Interface           | 32 |

|---------|------------------------------------|----|

| 4.11.1  | Stereo Audio Output Ports          | 32 |

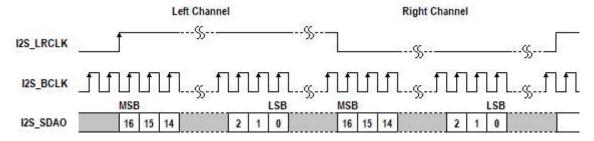

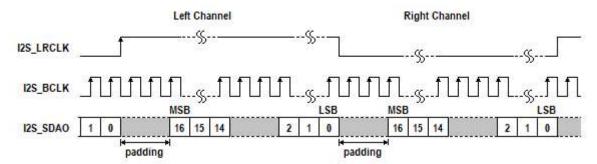

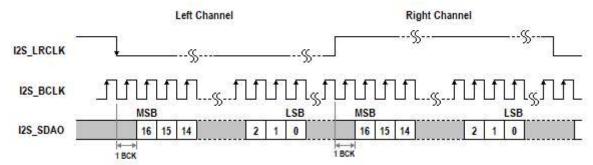

| 4.11.2  | I2S Interface                      | 32 |

| 4.12 W  | atchdog                            | 33 |

| 4.13 Sy | stem Clock                         | 34 |

| 4.13.1  | Clock Source                       |    |

| 4.13.2  | Phase Locked Loop                  | 34 |

| 4.13.3  | Clock Enable                       | 34 |

| 4.13.4  | Clock Frequency                    | 34 |

| 4.14 In | terrupt                            | 35 |

| 4.15 Ge | eneral Purpose IO (GPIO) Pins      | 35 |

| 4.16 Mi | scellaneous Control                | 35 |

| 4.16.1  | Backlight Control Pin              | 35 |

| 4.16.2  | DISP Control Pin                   | 35 |

| 4.17 Pc | ower Management                    | 35 |

| 4.17.1  | Power Supply                       | 35 |

| 4.17.2  | Internal Regulator and POR         | 36 |

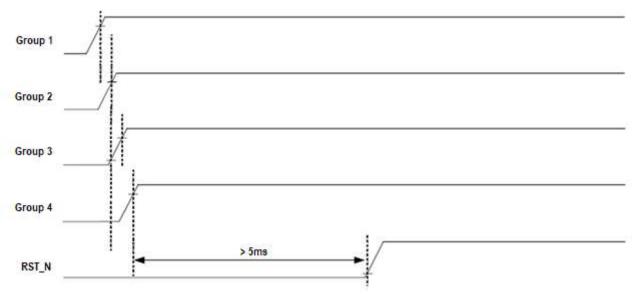

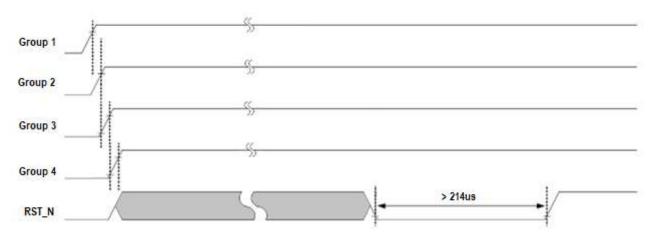

| 4.17.3  | Reset and Boot-up Sequence         | 36 |

| 4.17.4  | Power Modes                        | 38 |

| 4.17.5  | Power up Default Pin State         | 39 |

| 4.17.6  | Drive Strength                     | 40 |

| 4.17.7  | Slew Rate                          | _  |

| 4.17.8  | Pin state                          | 40 |

| 4.18 Pi | n Status at Different Power States | 40 |

| 5 Dev   | vice Characteristics and Ratings   | 44 |

| 5.1 Ab  | osolute Maximum Ratings            | 44 |

| 5.2 ES  | D and Latch-up Specifications      | 44 |

| 5.3 DO  | C Characteristics                  | 44 |

| 5.4 AC  | C Characteristics                  | 48 |

| 5.4.1   | Input Clock                        | 48 |

| 5.4.2   | QSPI Host Interface I/O Timing     |    |

| 5.4.3   | QSPI Flash Interface I/O Timing    | 49 |

| 5.4.4   | LVDSTX Timing                      | 49 |

| 5.4.5   | LVDSRX Timing                      | 50 |

|         |                                    |    |

| 5.4.6   | Audio Output Timing                          | 50 |

|---------|----------------------------------------------|----|

| 6 Ар    | plication Information                        | 52 |

| 6.1 I   | nput Clock                                   | 52 |

| 6.1.1   | Crystal Source                               | 52 |

| 6.1.2   | PCB Design Guidelines for Crystal Oscillator | 52 |

| 6.1.3   | Phase Locked Loop                            | 52 |

| 6.2 V   | ideo Input / Outputs                         | 53 |

| 6.2.1   | PCB Design Guidelines for LVDS channels      | 53 |

| 6.3 D   | DDR Interface                                | 53 |

| 6.3.1   | PCB Design Guidelines for DDR3/DDR3L         | 53 |

| 6.3.2   | PCB Design Guidelines for LPDDR2             | 54 |

| 7 Pa    | ckage Parameters                             | 56 |

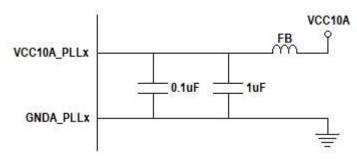

| 7.1 P   | art Marking                                  | 56 |

| 7.1.1   | Top Side                                     |    |

| 7.1.2   | Bottom Side                                  |    |

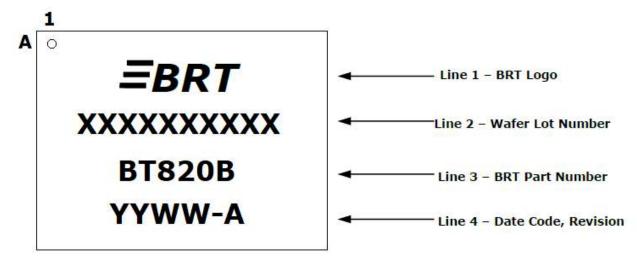

| 7.2 3   | 29 BALLS LFBGA Package Dimensions            | 57 |

| 8 Co    | ntact Information                            | 59 |

|         | dix A – References                           |    |

|         |                                              |    |

| _       | yms and Abbreviations                        |    |

| Appen   | dix B – List of Figures and Tables           | 61 |

| Appen   | dix C – Revision History                     | 63 |

| Interna | al Revision History                          | 64 |

|         |                                              |    |

# 3 Device Pin Out and Signal Description

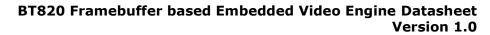

# 3.1 BT820B Package Pin Out

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19

Figure 3 - Pin Configuration BT820B 329 BALLS LFBGA (Transparent Top View)

# 3.2 Pin Description

| Ball Number     | Ball Name | Туре     | Description                                                                                                                                    |

|-----------------|-----------|----------|------------------------------------------------------------------------------------------------------------------------------------------------|

| MCU Interface   |           | <b>'</b> |                                                                                                                                                |

| W6              | SCK       | I        | SPI clock input                                                                                                                                |

| V7              | SS_N      | I        | SPI slave select input                                                                                                                         |

| V6              | MISO      | I/O      | SPI Single mode: SPI MISO output<br>SPI Dual/Quad mode: SPI data line 1                                                                        |

| W7              | MOSI      | I/O      | SPI Single mode: SPI MOSI input                                                                                                                |

|                 |           |          | SPI Dual/Quad mode: SPI data line 0 SPI Single mode: General purpose IO 0                                                                      |

| W8              | GPIO0/IO2 | I/O      | SPI Quad mode: SPI data line 2                                                                                                                 |

| V8              | GPIO1/IO3 | I/O      | SPI Single mode: General purpose IO 1<br>SPI Quad mode: SPI data line 3                                                                        |

| V9              | INT_N     | OD/O     | Interrupt to host, open drain output (default) or push-<br>pull output, active low                                                             |

| U9              | RST_N     | I        | Global reset pin. Connect to MCU GPIO for hardware reset function, or pull up to VCCIO1 through 47 K $\Omega$ resistor and 1 $\mu$ F to ground |

| Flash Interface |           | ·        |                                                                                                                                                |

| B5              | SPIM_SCLK | 0        | SPI flash clock output line                                                                                                                    |

| В3              | SPIM_SS_N | 0        | SPI flash chip-select output line                                                                                                              |

| А3              | SPIM_MISO | I/O      | SPI flash MISO line                                                                                                                            |

| A4              | SPIM_MOSI | I/O      | SPI flash MOSI line                                                                                                                            |

| B4              | SPIM_IO2  | I/O      | SPI flash IO2 line                                                                                                                             |

| A5              | SPIM_IO3  | I/O      | SPI flash IO3 line                                                                                                                             |

| SD Card Interfa | се        |          |                                                                                                                                                |

| C19             | SDCD      | I        | SD Card Detect                                                                                                                                 |

| B18             | SDCLK     | 0        | SD Card serial clock output                                                                                                                    |

| B17             | SDCMD     | I/O      | SD Card Command signal                                                                                                                         |

| A16             | SDWP      | I        | SD Card Write protection                                                                                                                       |

| B19             | SDD0      | I/O      | SD Card Data bus line 0                                                                                                                        |

| C18             | SDD1      | I/O      | SD Card Data bus line 1                                                                                                                        |

| A17             | SDD2      | I/O      | SD Card data bus line 2                                                                                                                        |

| A18             | SDD3      | I/O      | SD Card Data bus line 3                                                                                                                        |

| DDR Interface   |           |          |                                                                                                                                                |

| P19             | CK        | 0        | DDR DRAM clock differential P signal                                                                                                           |

| P18             | СКВ       | 0        | DDR DRAM clock differential N signal                                                                                                           |

| L17             | DQ0       | I/O      | DDR DRAM data bus bit 0                                                                                                                        |

| J18             | DQ1       | I/O      | DDR DRAM data bus bit 1                                                                                                                        |

| L19             | DQ2       | I/O      | DDR DRAM data bus bit 2                                                                                                                        |

| H18             | DQ3       | I/O      | DDR DRAM data bus bit 3                                                                                                                        |

| L18             | DQ4       | I/O      | DDR DRAM data bus bit 4                                                                                                                        |

| H17             | DQ5       | I/O      | DDR DRAM data bus bit 5                                                                                                                        |

| Ball Number | Ball Name | Туре | Description                                   |

|-------------|-----------|------|-----------------------------------------------|

| M18         | DQ6       | I/O  | DDR DRAM data bus bit 6                       |

| J19         | DQ7       | I/O  | DDR DRAM data bus bit 7                       |

| F17         | DQ8       | I/O  | DDR DRAM data bus bit 8                       |

| E18         | DQ9       | I/O  | DDR DRAM data bus bit 9                       |

| G18         | DQ10      | I/O  | DDR DRAM data bus bit 10                      |

| D18         | DQ11      | I/O  | DDR DRAM data bus bit 11                      |

| G17         | DQ12      | I/O  | DDR DRAM data bus bit 12                      |

| D17         | DQ13      | I/O  | DDR DRAM data bus bit 13                      |

| G19         | DQ14      | I/O  | DDR DRAM data bus bit 14                      |

| E19         | DQ15      | I/O  | DDR DRAM data bus bit 15                      |

| K19         | DQS0      | I/O  | DDR DRAM dqs for lower data byte              |

| K18         | DQSB0     | I/O  | DDR DRAM dqs# (diff mode) for lower data byte |

| F19         | DQS1      | I/O  | DDR DRAM dqs for upper data byte              |

| F18         | DQSB1     | I/O  | DDR DRAM dqs# (diff mode) for upper data byte |

| J17         | DM0       | 0    | DDR DRAM data mask for lower data byte        |

| D19         | DM1       | 0    | DDR DRAM data mask for lower data byte        |

| V18         | ADDR0     | 0    | DDR DRAM address bit 0                        |

| U18         | ADDR1     | 0    | DDR DRAM address bit 1                        |

| V17         | ADDR2     | 0    | DDR DRAM address bit 2                        |

| V15         | ADDR3     | 0    | DDR DRAM address bit 3                        |

| R19         | ADDR4     | 0    | DDR DRAM address bit 4                        |

| W16         | ADDR5     | 0    | DDR DRAM address bit 5                        |

| T19         | ADDR6     | 0    | DDR DRAM address bit 6                        |

| V16         | ADDR7     | 0    | DDR DRAM address bit 7                        |

| T18         | ADDR8     | 0    | DDR DRAM address bit 8                        |

| W17         | ADDR9     | 0    | DDR DRAM address bit 9                        |

| T17         | ADDR10    | 0    | DDR DRAM address bit 10                       |

| U19         | ADDR11    | 0    | DDR DRAM address bit 11                       |

| V19         | ADDR12    | 0    | DDR DRAM address bit 12                       |

| W18         | ADDR13    | 0    | DDR DRAM address bit 13                       |

| R17         | ADDR14    | 0    | DDR DRAM address bit 14                       |

| W15         | BA0       | 0    | DDR DRAM bank address bit 0                   |

| R18         | BA1       | 0    | DDR DRAM bank address bit 1                   |

| U17         | BA2       | 0    | DDR DRAM bank address bit 2                   |

| W13         | RAS       | 0    | DDR DRAM command input                        |

| V13         | CAS       | 0    | DDR DRAM command input                        |

| W14         | WE        | 0    | DDR DRAM command input                        |

| N19         | CKE       | 0    | DDR DRAM clock enable                         |

| Ball Number  | Ball Name       | Туре | Description                                                                                                                         |

|--------------|-----------------|------|-------------------------------------------------------------------------------------------------------------------------------------|

| U14          | CS0             | 0    | DDR DRAM chip select bit 0                                                                                                          |

| V14          | CS1             | 0    | DDR DRAM chip select bit 1                                                                                                          |

| U13          | ODT0            | 0    | DDR DRAM ODT resistor control bit 0                                                                                                 |

| U12          | ODT1            | 0    | DDR DRAM ODT resistor control bit 1                                                                                                 |

| N18          | RST_N_DDR       | 0    | DDR DRAM reset for DDR3 mode                                                                                                        |

| M19          | VREF0           | AI/O | DDR reference voltage for lower data byte receivers. Connect a voltage that is half the voltage of VCCIO_DDR.                       |

| H19          | VREF1           | AI/O | DDR reference voltage for lower data byte receivers. Connect a voltage that is half the voltage of VCCIO_DDR.                       |

| W12          | RDRVDN          | AI/O | DDR pad to precise external resistor for pull-down driver. Tie to DDR I/O power via $240\Omega$ external resistor with 1% tolerance |

| V12          | RDRVUP          | AI/O | DDR pad to precise external resistor for pull-up driver. Tie to GND via $240\Omega$ external resistor with $1\%$ tolerance          |

| Video Output |                 |      |                                                                                                                                     |

| H1           | DISP            | 0    | LCD display general purpose control (e.g., enable/reset) signal                                                                     |

| H2           | BACKLIGHT       | 0    | LED backlight brightness PWM control signal                                                                                         |

| M1           | LVDSTX0_CLK_N   | 0    | LVDS TX channel 0 clock differential N signal                                                                                       |

| M2           | LVDSTX0_CLK_P   | 0    | LVDS TX channel 0 clock differential P signal                                                                                       |

| U1           | LVDSTX1_CLK_N   | 0    | LVDS TX channel 1 clock differential N signal                                                                                       |

| U2           | LVDSTX1_CLK_P   | 0    | LVDS TX channel 1 clock differential P signal                                                                                       |

| J1           | LVDSTX0_DATA0_N | 0    | LVDS TX channel 0 data bit 0 differential N signal                                                                                  |

| J2           | LVDSTX0_DATA0_P | 0    | LVDS TX channel 0 data bit 0 differential P signal                                                                                  |

| K1           | LVDSTX0_DATA1_N | 0    | LVDS TX channel 0 data bit 1 differential N signal                                                                                  |

| K2           | LVDSTX0_DATA1_P | 0    | LVDS TX channel 0 data bit 1 differential P signal                                                                                  |

| L1           | LVDSTX0_DATA2_N | 0    | LVDS TX channel 0 data bit 2 differential N signal                                                                                  |

| L2           | LVDSTX0_DATA2_P | 0    | LVDS TX channel 0 data bit 2 differential P signal                                                                                  |

| N1           | LVDSTX0_DATA3_N | 0    | LVDS TX channel 0 data bit 3 differential N signal                                                                                  |

| N2           | LVDSTX0_DATA3_P | 0    | LVDS TX channel 0 data bit 3 differential P signal                                                                                  |

| P1           | LVDSTX1_DATA0_N | 0    | LVDS TX channel 1 data bit 0 differential N signal                                                                                  |

| P2           | LVDSTX1_DATA0_P | 0    | LVDS TX channel 1 data bit 0 differential P signal                                                                                  |

| R1           | LVDSTX1_DATA1_N | 0    | LVDS TX channel 1 data bit 1 differential N signal                                                                                  |

| R2           | LVDSTX1_DATA1_P | 0    | LVDS TX channel 1 data bit 1 differential P signal                                                                                  |

| T1           | LVDSTX1_DATA2_N | 0    | LVDS TX channel 1 data bit 2 differential N signal                                                                                  |

| T2           | LVDSTX1_DATA2_P | 0    | LVDS TX channel 1 data bit 2 differential P signal                                                                                  |

| V1           | LVDSTX1_DATA3_N | 0    | LVDS TX channel 1 data bit 3 differential N signal                                                                                  |

| V2           | LVDSTX1_DATA3_P | 0    | LVDS TX channel 1 data bit 3 differential P signal                                                                                  |

| Video Input  |                 | •    | ,                                                                                                                                   |

| A12          | LVDSRX0_CLK_N   | I    | LVDS RX channel 0 clock differential N signal                                                                                       |

| Ball Number    | Ball Name        | Туре | Description                                                               |

|----------------|------------------|------|---------------------------------------------------------------------------|

| B12            | LVDSRX0_CLK_P    | I    | LVDS RX channel 0 clock differential P signal                             |

| A7             | LVDSRX1_CLK_N    | I    | LVDS RX channel 1 clock differential N signal                             |

| В7             | LVDSRX1_CLK_P    | I    | LVDS RX channel 1 clock differential P signal                             |

| A15            | LVDSRX0_DATA0_N  | I    | LVDS RX channel 0 data bit 0 differential N signal                        |

| B15            | LVDSRX0_DATA0_P  | I    | LVDS RX channel 0 data bit 0 differential P signal                        |

| A14            | LVDSRX0_DATA1_N  | I    | LVDS RX channel 0 data bit 1 differential N signal                        |

| B14            | LVDSRX0_DATA1_P  | I    | LVDS RX channel 0 data bit 1 differential P signal                        |

| A13            | LVDSRX0_DATA2_N  | I    | LVDS RX channel 0 data bit 2 differential N signal                        |

| B13            | LVDSRX0_DATA2_P  | I    | LVDS RX channel 0 data bit 2 differential P signal                        |

| A11            | LVDSRX0_DATA3_N  | I    | LVDS RX channel 0 data bit 3 differential N signal                        |

| B11            | LVDSRX0_DATA3_P  | I    | LVDS RX channel 0 data bit 3 differential P signal                        |

| A10            | LVDSRX1_DATA0_N  | I    | LVDS RX channel 1 data bit 0 differential N signal                        |

| B10            | LVDSRX1_DATA0_P  | I    | LVDS RX channel 1 data bit 0 differential P signal                        |

| A9             | LVDSRX1_DATA1_N  | I    | LVDS RX channel 1 data bit 1 differential N signal                        |

| В9             | LVDSRX1_DATA1_P  | I    | LVDS RX channel 1 data bit 1 differential P signal                        |

| A8             | LVDSRX1_DATA2_N  | I    | LVDS RX channel 1 data bit 2 differential N signal                        |

| B8             | LVDSRX1_DATA2_P  | I    | LVDS RX channel 1 data bit 2 differential P signal                        |

| A6             | LVDSRX1_DATA3_N  | I    | LVDS RX channel 1 data bit 3 differential N signal                        |

| В6             | LVDSRX1_DATA3_P  | I    | LVDS RX channel 1 data bit 3 differential P signal                        |

| C11            | LVDSRX0_RPI      | I    | LVDS RX channel 0 bias. Connects 3.5 K $\Omega$ external resistor to GND. |

| C9             | LVDSRX1_RPI      | I    | LVDS RX channel 1 bias. Connects 3.5 K $\Omega$ external resistor to GND. |

| Touch Control  | T                | 1    | T                                                                         |

| U4             | GPIO3            | I/O  | General purpose IO 3                                                      |

| V4             | GPIO4            | I/O  | General purpose IO 4                                                      |

| W4             | GPIO5 / TP_SCL   | I/O  | General purpose IO 5 / I2S_SCL for Touch Control                          |

| U5             | GPIO6 / TP_SDA   | I/O  | General purpose IO 6 / I2C_SDA for Touch Control                          |

| V5             | GPIO7 / TP_INT_N | I/O  | General purpose IO 7 / INT_N for Touch Control                            |

| W5             | GPIO8 / TP_RST_N | I/O  | General purpose IO 8 / RST_N for Touch Control                            |

| Audio Control  | I                | 1    |                                                                           |

| F1             | AUDIO_L          | 0    | Audio Delta-Sigma left output                                             |

| E1             | AUDIO_R          | 0    | Audio Delta-Sigma right output                                            |

| G1             | I2S_BCLK         | I    | I2S bit clock                                                             |

| F2             | I2S_LRCLK        | I    | I2S left/right clock                                                      |

| G2             | I2S_SDAO         | 0    | I2S serial data output                                                    |

| GPIO Interface |                  | 1    |                                                                           |

| W9             | GPIO2            | I/O  | General purpose IO 2                                                      |

| A2             | GPIO9 / TIO3     | I/O  | General purpose IO 9                                                      |

| B2             | GPIO10 / TIO4    | I/O  | General purpose IO 10                                                     |

| Ball Number                                                                                   | Ball Name     | Туре | Description                                                                                            |  |

|-----------------------------------------------------------------------------------------------|---------------|------|--------------------------------------------------------------------------------------------------------|--|

| C2                                                                                            | GPIO11 / TIO5 | I/O  | General purpose IO 11                                                                                  |  |

| D2                                                                                            | GPIO12 / TIO6 | I/O  | General purpose IO 12                                                                                  |  |

| B1                                                                                            | GPIO13 / TIO7 | I/O  | General purpose IO 13                                                                                  |  |

| C1                                                                                            | GPIO14 / TIO8 | I/O  | General purpose IO 14                                                                                  |  |

| D1                                                                                            | GPIO15 / TIO9 | I/O  | General purpose IO 15                                                                                  |  |

| Clock Interface                                                                               |               | •    |                                                                                                        |  |

| W10                                                                                           | X1/CLK        | AI   | Crystal oscillator or clock input. 3.3V peak input allowed                                             |  |

| W11                                                                                           | X2            | AI/O | Crystal oscillator output                                                                              |  |

| Power                                                                                         |               |      |                                                                                                        |  |

| G5, H5, J5                                                                                    | VCC33A_REG    | Р    | 3.3V Analog supply for Linear Regulator. A 47uF capacitor must be connected between VCC33A_REG and GND |  |

| K5, L5, M5                                                                                    | VCC10A_REG    | Р    | 1.0V output voltage from Linear Regulator. Connect a 3.3uF decoupling capacitor                        |  |

| D13, E7, F4,<br>H13, L4 M4,<br>M13, T8 R11,<br>P5                                             | VCC10K        | Р    | 1.0V digital core power supply                                                                         |  |

| T5, U7                                                                                        | VCCIO1        | Р    | I/O power supply for host interface pins. Support 1.8V, 2.5V or 3.3V                                   |  |

| D4, E3, G3                                                                                    | VCCIO2        | Р    | 3.3V I/O power supply for Display, I2S and Audio                                                       |  |

| C5, E6                                                                                        | VCCIO3        | Р    | I/O power supply for SPIM interface pins. Support 1.8V, 2.5V or 3.3V                                   |  |

| B16, C17                                                                                      | VCCIO4        | Р    | I/O power supply for SD interface pins. Support 1.8V, 2.5V or 3.3V                                     |  |

| K3, N3, T3                                                                                    | VCC33A_LVDSTX | Р    | 3.3V Analog supply for LVDS TX                                                                         |  |

| C6, C8, C10,<br>C12                                                                           | VCC33A_LVDSRX | Р    | 3.3V Analog supply for LVDS RX                                                                         |  |

| C7, D14, E9,<br>E12                                                                           | VCC10A_LVDSRX | Р    | 1.0V Analog supply for LVDS RX                                                                         |  |

| E14, J13, L13,<br>T10, N13                                                                    | VCC10K_DDR    | Р    | 1.0V digital power supply for DDR PHY                                                                  |  |

| D16, E17, F16,<br>G16, H16, J15,<br>J16, K17, L16,<br>M17, T12, T13,<br>T14, T16, U11,<br>U16 | VCCIO_DDR     | P    | Digital I/O power supply for DDR PHY                                                                   |  |

| N17, P17                                                                                      | VCCIO_DDR_CK  | Р    | Digital I/O power supply for DDR CK/CKB and CKE                                                        |  |

| R6                                                                                            | VCC33A_OTP    | Р    | 3.3V I/O power supply for OTP                                                                          |  |

| V10                                                                                           | VCC33A_OSC    | Р    | 3.3V Analog power supply for OSC pad                                                                   |  |

| R9                                                                                            | VCC10A_PLL1   | Р    | 1.0V Analog power supply for PLL1                                                                      |  |

| W3                                                                                            | VCC10A_PLL2   | Р    | 1.0V Analog power supply for PLL2                                                                      |  |

| N15                                                                                           | VCC10A_PLL3   | Р    | 1.0V Analog power supply for PLL3                                                                      |  |

| R15                                                                                           | VCC10A_PLL4   | Р    | 1.0V Analog power supply for PLL4                                                                      |  |

| Ground                                                                                        |               |      |                                                                                                        |  |

| A1, A19, C13,<br>C15, C16, D5,<br>D15, E2, E4,<br>E5, E8, E13,                                | GNDK          | Р    | Digital Ground                                                                                         |  |

| Ball Number                                                                                                                                                                                                                                                                                                                                                      | Ball Name | Туре | Description                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|----------------------------------------|

| E15, E16, F3, F5, F15, G4, G7, G8, G9, G10, G11 G12, G13, G15 H7, H8, H9, H10, H11, H12, H15, J7, J8, J9, J10, J11, J12, K7, K8, K9, K10, K11, K12, K13, K15, K16, L3, L7, L8, L9, L10, L11, L12, L15, M3, M7, M8, M9, M10, M11, M12, M16, N5, N7, N8, N9, N10, N11, N12, N16, P15, P16, R5, R10, R12, R13, R16, T4, T9, T11, T15, U6, U8, U10, U15, V3, W1, W19 |           |      |                                        |

| C14, D6, D7,<br>D8, D10, D12,<br>E10, E11, J3,<br>P3, U3                                                                                                                                                                                                                                                                                                         | GNDA_LVDS | Р    | LVDS Analog Ground                     |

| ,<br>R7                                                                                                                                                                                                                                                                                                                                                          | GNDA_OTP  | Р    | Analog ground for OTP                  |

| V11                                                                                                                                                                                                                                                                                                                                                              | GNDA_OSC  | Р    | Analog ground for OSC                  |

| R8                                                                                                                                                                                                                                                                                                                                                               | GNDA_PLL1 | Р    | Analog ground for PLL1                 |

| W2                                                                                                                                                                                                                                                                                                                                                               | GNDA_PLL2 | Р    | Analog ground for PLL2                 |

| M15                                                                                                                                                                                                                                                                                                                                                              | GNDA_PLL3 | Р    | Analog ground for PLL3                 |

| R14                                                                                                                                                                                                                                                                                                                                                              | GNDA_PLL4 | Р    | Analog ground for PLL4                 |

| Test Pins                                                                                                                                                                                                                                                                                                                                                        |           |      |                                        |

| C4                                                                                                                                                                                                                                                                                                                                                               | TIO0      | I/O  | Test pin bit 0. To be left unconnected |

| C3                                                                                                                                                                                                                                                                                                                                                               | TIO1      | I/O  | Test pin bit 1. To be left unconnected |

| D3                                                                                                                                                                                                                                                                                                                                                               | TIO2      | I/O  | Test pin bit 2. To be left unconnected |

| No Connections                                                                                                                                                                                                                                                                                                                                                   |           |      |                                        |

| D9, D11, H3,<br>H4, J4, N4,<br>P4, R3, R4,<br>T6, T7, K4                                                                                                                                                                                                                                                                                                         | NC        |      | No Connections                         |

Table 2 - BT820B Pin Description

#### Note:

P : Power or ground

I : Input O : Output

OD : Open drain output

I/O : Bi-direction Input and Output AI/O : Analog Input and Output

NC : No connection and must be left open/floating

# **4 Functional Description**

The BT820 is a single chip, embedded video controller with the following functional blocks:

- Graphics Engine

- LVDS Transmit Interface

- LVDS Receive Interface

- DDR DRAM Interface

- Quad SPI Host Interface

- Quad SPI Flash Interface

- SD Card Host Controller

- Touch Engine and Interface

- Audio Engine

- Audio Outputs / Interface

- Watchdog Timer

- System Clock

- General Purpose IO (GPIO) Pins

- Power Management

The functions for each block are briefly described in the following subsections.

# 4.1 Graphics Engine

#### 4.1.1 Introduction

The graphics engine executes the display list once for every frame. The BT820 includes a 16Kbytes double-buffered memory within its graphics engine, dedicated to storing display list commands. The display list can contain between 1 and 4096 commands, each of which sets the graphics state, performs a drawing action, or controls the execution flow within the list. The graphics engine then executes the primitive objects in the display list and constructs the display frame buffer.

Main features of the graphics engine are:

- The primitive objects supported by the graphics processor are lines, points, rectangles, bitmaps (comprehensive set of formats), text display, plotting bar graph, edge strips, line strips, etc

- Operations such as stencil test, alpha blending and masking are useful for creating a rich set of

effects such as shadow, transitions, reveals, fades, and wipes

- · Anti-aliasing of the primitive objects (except bitmaps) gives a smoothing effect to the viewer

- Bitmap transformations enable operations such as translate, scale, and rotate

- Display pixels are plotted with 1/16<sup>th</sup> pixel resolution

- Four levels of graphics states

- Tag buffer for touch detection

The graphics engine also supports customized built-in widgets and functionalities. The graphics engine reads and executes the commands from the MCU. This is done by accessing the command FIFO. Refer to BRT AN086 BT82X Series Programming Guide for details to access the graphics engine.

The graphics engine used in BT820 has many improvements over the one in BT81x series:-

- Unified memory model, supporting an address space up to 512MBytes

- 24-bit RGB framebuffer up to 2048 x 2048 pixels

- Render-to-bitmap capability

- Hardware INFLATE engine

- Hardware PNG decode engine

- YCbCr format support

- 24-bit RGB and 32-bit RGBA bitmap support

- Full-speed palette bitmaps, and 32-bit RGBA palettes

#### Other features supported are:

Drawing of widget such as ARC, buttons, clock, keys, gauges, text displays, progress bars, sliders, toggle switches, dials, gradients, etc

Document No.: BRT\_000427 Clearance No.:BRT#214

- JPEG and motion-JPEG decode

- Snapshot feature to capture the current graphics display

- ASTC decode

# 4.1.2 Hardware INFLATE Engine

The BT820 features a hardware INFLATE Engine that decompresses application-specific assets that may be supplied in the command buffer, the media fifo, or from the external flash, and transfers the results to either the graphics engine or DDR memory. The hardware INFLATE engine greatly accelerates the decompression process.

These assets can be compressed using the Asset Compressor feature in the EVE Asset Builder.

## 4.1.3 Hardware PNG decode Engine

The hardware PNG decode engine featured in the BT820 is designed to efficiently decode the Portable Network Graphics (PNG) images.

#### 4.1.4 YCbCr Format

BT820 supports YCbCr encoding and YCbCr decoding. The YCbCr format is a lossy pixel format using 1 byte per pixel. The pixels are encoded in  $2 \times 2$  blocks, each taking 32 bits of memory.

| a | ь |

|---|---|

| c | d |

The YCbCr is particularly suited to JPEG output, but is also effective as a framebuffer format with very little loss in quality. There are three encoding variants, depending on the distribution of Y pixels in the quad. The 5-bit chroma encoding is most frequently used, with 6- and 8-bit chroma used for quad with similar Y values. This improves color fidelity in image regions with little luminance detail.

#### 4.1.5 Render Engine

The BT820 render engine excels in memory-to-memory operations, leveraging local memory access for bulk memory and image processing tasks. This local optimization translates to significant speed advantage in data handling and rendering tasks, avoiding the SPI bottleneck inherent in using the microcontroller.

The render engine supports a maximum bitmap size of 2048 x 2048 and a maximum bitmap linestride of 8192 bytes.

#### 4.1.6 ASTC

ASTC stands for  $\bf A$ daptive  $\bf S$ calable  $\bf T$ exture  $\bf C$ ompression, an open standard developed by ARM for use in mobile GPUs.

ASTC is a block-based lossy compression format. The compressed image is divided into a number of blocks of uniform size, which makes it possible to quickly determine which block a given texel (unit of a texture map) resides in. Each block has a fixed memory footprint of 128 bits, but these bits can represent varying numbers of texels (the block footprint).

Block footprint sizes are not confined to power-of-two, and are also not confined to be square. For 2D formats, the block dimensions range from 4 to 12 texels.

Using ASTC for the large ROM fonts can save considerable space. Encoding the four largest fonts in ASTC 8x8 formats gives no noticable loss in quality and reduces the ROM size from 1 Mbytes to about 640 Kbytes.

#### 4.1.7 ROM and RAM Fonts

The BT820 has built-in ROM character bitmaps as font metrics. The graphics engine can use these metrics when drawing text fonts. There are a total of 19 ROM fonts, numbered with font handle 16-34. Font 31-34 are large ROM fonts encoded in ASTC 8x8 format. The user can define and load customized font metrics into the DDR memory or external flash, making it possible to support a full range of unicode characters with UTF-8 coding points.

The BT820 recognizes two in-memory font structures. A legacy format handles fonts with code points 0x0 to 0x7F. An extended format can handle fonts with a full range of unicode code points.

#### 4.1.7.1 Legacy Format

Each ROM font metric block has a 148 byte font table which defines the parameters of the font and the pointer of font image. The Legacy font metric block is listed in Table 3.

| Address Offset | Size | Value                                        |  |  |

|----------------|------|----------------------------------------------|--|--|

| 0              | 128  | Width of each font character, in pixels      |  |  |

| 128            | 2    | Font bitmap format, for example L1, L4 or L8 |  |  |

| 130            | 2    | Font flag (see below)                        |  |  |

| 132            | 4    | Font line stride, in bytes                   |  |  |

| 136            | 4    | Font width, in pixels                        |  |  |

| 140            | 4    | Font height, in pixels                       |  |  |

| 144            | 4    | Pointer to font graphic data in memory       |  |  |

Table 3 - Legacy Format

#### 4.1.7.2 Extended Format

The font for the Extended block is variable-sized, depending on the number of characters.

Refer to BRT AN086 BT82X Series Programming Guide for details on how to access the Extended format.

#### 4.1.7.3 ROM fonts

The ROM fonts are loaded at startup into handles 16-34. These fonts can be loaded into arbitrary handles and the font handles can be reset to their startup defaults.

Each font contains 95 printable ASCII characters ranging from 0x20 to 0x7E, which correspond to their respective ASCII values.

Table 4 lists the ROM font handles.

| handle | em-width | em-height | note                                         |

|--------|----------|-----------|----------------------------------------------|

| 16     | 8        | 8         | 1-bit, monospace                             |

| 17     | 8        | 8         | 1-bit, monospace (Extended ASCII characters) |

| 18     | 8        | 16        | 1-bit, monospace                             |

| 19     | 8        | 16        | 1-bit, monospace (Extended ASCII characters) |

| 20     | 10       | 13        | 1-bit, proportional                          |

| 21     | 13       | 17        | 1-bit, proportional                          |

| 22     | 14       | 20        | 1-bit, proportional                          |

| 23     | 17       | 22        | 1-bit, proportional                          |

| 24     | 24       | 29        | 1-bit, proportional                          |

| 25     | 30       | 38        | 1-bit, proportional                          |

| 26     | 14       | 16        | anti-aliased, proportional with kerning      |

| 27     | 15       | 18        | anti-aliased, proportional with kerning      |

| 28     | 18       | 22        | anti-aliased, proportional with kerning      |

| 29     | 22       | 27        | anti-aliased, proportional with kerning      |

| 30     | 28       | 33        | anti-aliased, proportional with kerning      |

| 31     | 38       | 46        | anti-aliased, proportional with kerning      |

| 32     | 48       | 58        | anti-aliased, proportional with kerning      |

| _ |    |    |    |                                         |

|---|----|----|----|-----------------------------------------|

|   | 33 | 62 | 74 | anti-aliased, proportional with kerning |

|   | 34 | 83 | 98 | anti-aliased, proportional with kerning |

Table 4 - ROM font handles

Note: The em-width and em-height are the size of uppercase "M" character in pixels.

A 1-bit monospace font is a type of font where each character is displayed using only two colours (black and white), and every character occupies the same horizontal space. In contrast, a 1-bit proportional font also uses two colours, but the characters have varying widths, taking up only as much horizontal space as needed, which enhances readability and aesthetic appeal.

Anti-aliased proportional fonts with kerning are a type of proportional font where the anti-aliasing technique smooths the edges of characters, reducing jagged edges on diagonal or curved lines by blending them with the background. Kerning adjusts the spacing between specific pairs of characters to ensure consistent and balanced spacing, making the text look more professional and easier to read.

#### 4.1.7.4 Using Custom Font

The custom fonts are loaded into the DDR memory and the new fonts can be registered with handle 0-63 using internal commands. Refer to BRT AN086 BT82X Series Programming Guide for details on how to program the custom fonts.

# 4.2 Video Outputs

The BT820 support video streams up to 1920x1200 resolution at 60fps. The video output consists of the ExtSync and the LVDS transmit interface.

## 4.2.1 ExtSync

The function of the ExtSync is to bridge the graphics engine output to the LVDS transmit interface at different scanout frequencies. It achieves this by buffering the video streams and then transferring them to the LVDS transmit interface with the generated LVDSTX clock.

#### 4.2.2 LVDS Transmit Interface

The BT820 implements 2 LVDS channels of 4 data lanes each to transmit 18 or 24-bit RGB signals. The BT820 supports a programmable PCLK, up to 83.2MHz. This allows the BT820 to support a wider range of display panels, up to 1920x1200 resolution at 60fps.

Four video modes are implemented:

- VESA / Format 2 Mapping for 18-bit RGB

- VESA / Format 2 Mapping for 24-bit RGB

- JEIDA / Format 1 Mapping for 18-bit RGB

- JEIDA / Format 1 Mapping for 24-bit RGB

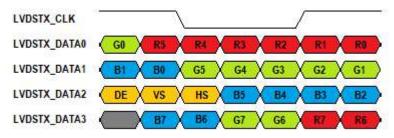

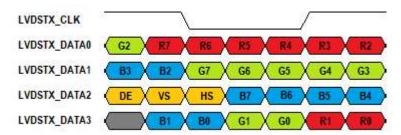

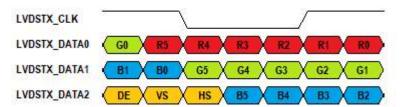

Figure 4 shows the video formats for VESA / Format 2 Mappings for 24-bit RGB, Figure 5 shows the video formats for JEIDA / Format 1 Mappings for 24-bit RGB, Figure 6 shows the video formats for JEIDA / Format 1 Mapping for 18-bit RGB.

Figure 4 - VESA / Format 2 Mapping for 24-bit RGB

Figure 5 - JEIDA / Format 1 Mapping for 24-bit RGB

Figure 6 - JEIDA / Format 1 Mapping for 18-bit RGB

VESA / Format 2 Mapping for 24-bit RGB is implemented as the default for both LVDS channels

BT820 supports 2 LVDS transmit channels, LVDSTX0 and LVDSTX1. When using dual channels LVDS display, LVDSTX0 is the odd channel while LVDSTX1 is the even channel. When using single channel LVDS display, only LVDSTX0 is operational.

#### 4.3 LVDS Receive Interface

The BT820 implements 2 LVDS channels of 4 data lanes to capture 18 or 24-bit RGB signals.

Three video modes are supported:

- VESA / Format 2 Mapping for 24-bit RGB

- JEIDA / Format 1 Mapping for 24-bit RGB

- JEIDA / Format 1 Mapping for 18-bit RGB

The BT820 can receive up to 1920x1200 resolution at 60fps

When capturing from dual LVDS channels, LVDSRX0 is the odd channel while LVDSRX1 is the even channel. When capturing from single LVDS channel, only LVDSRX0 is operational.

The maximum input clock for the LVDS receive channels are 144MHz at 72MHz system clock.

#### 4.4 DDR DRAM Interface

The BT820 includes a DDR DRAM interface to allow the core to use an external DDR DRAM as a frame buffer. This allows the core to speed up video processing and allows support for higher resolution processing.

BT820 supports external DDR3, DDR3L, and LPDDR2 DRAM with data rates of 933MT/s, 1066MT/s and 1333MT/s for DDR3 and DDR3L, and 800MT/s and 933MT/s for LPDDR2, with data bit width of 16 bits only. It supports DRAM size of 8 Gbit, 4 Gbit, 2 Gbit, 1 Gbit and 512 Mbit. Support for 8 Gbit DRAM is limited to the use of 2 ranks of 4 Gbit DRAM.

By default, the BT820 supports 1Gbit DDR3, DDR3L with data rate of 1333MT/s

The BT820 includes a configuration parameter in the host command to set the DDR type, size, and speed grade to match the physical memory. For detailed instructions on setting the DDR type, size, and speed grade, refer to the BRT AN086 BT82X Series Programming Guide.

Table 5 lists the tested DDR memories that are tested at 1333MT/s

| Brand   | Model             | Туре  | Description                                |

|---------|-------------------|-------|--------------------------------------------|

| Winbond | W631GU6NB-11      | DDR3L | 1Gbit (8M x 8 Banks x 16 Bit) DDR3L SDRAM  |

|         | W631GU6RB-11      | DDR3L | 1Gbit (8M x 8 Banks x 16 Bit) DDR3L SDRAM  |

|         | W634GU6RB-11      | DDR3L | 4Gbit (32M x 8 Banks x 16 Bit) DDR3L SDRAM |

| Micron  | MT41K256M16TW-107 | DDR3L | 4Gbit (32M x 8 Banks x 16 Bit) DDR3L SDRAM |

|         | MT41K128M16JT-107 | DDR3L | 2Gbit (16M x 8 Banks x 16 Bit) DDR3L SDRAM |

|         | MT41K64M16TW-107  | DDR3L | 1Gbit (8M x 8 Banks x 16 Bit) DDR3L SDRAM  |

Table 5 - List of tested DDR Memories

# 4.5 Quad SPI Host Interface

The BT820 uses the Quad SPI (QSPI) Host Interface, operating in slave mode, to communicate with the host microcontroller and microprocessor, which serve as the master.

The QSPI Host Interface operates up to 60MHz and only supports SPI mode 0, where data is sampled on the rising edge of SCK. The QSPI Host Interface can be configured as SPI Single, Dual, or Quad channel modes. By default, the interface operates in Single channel mode with the MOSI as input from the master and MISO as output to the master. The interface can then be configured to Dual or Quad channel mode by programming the internal registers of the BT820. Refer to BRT AN086 BT82X Series Programming Guide for details on how to reconfigure the QSPI Host Interface to Dual or Quad channel modes. In Dual channel mode, MISO (MSB) and MOSI are used as data ports while in Quad channel mode, IO3 (MSB), IO2, MISO and MOSI are used as data ports. The SPI data ports are bi-directional in Dual and Quad channel modes.

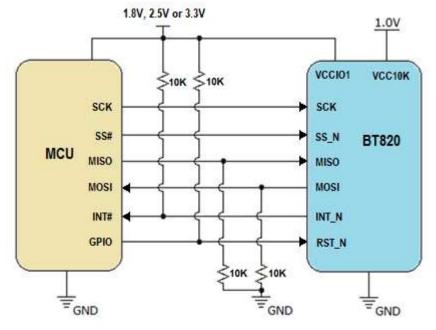

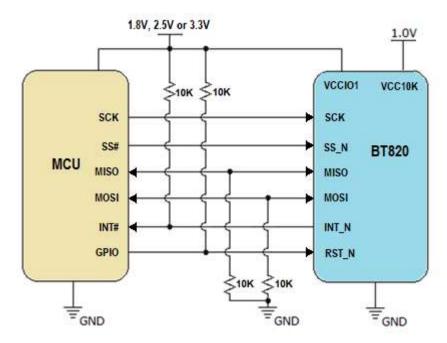

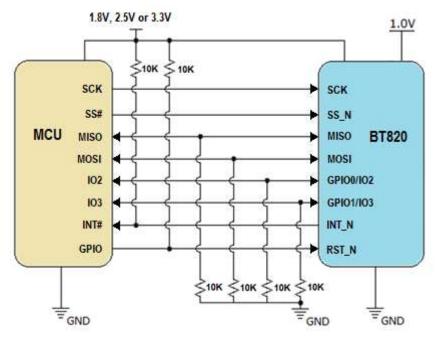

Figure 7 illustrates a direct connection to a MCU using Single SPI, Figure 8 illustrates a direct connection to a MCU using Dual SPI and Figure 9 illustrates a direct connection to a MCU using Quad SPI.

Figure 7 - QSPI Host Interface Using Single SPI Connection

Figure 8 – QSPI Host Interface Using Dual SPI Connection

Figure 9 - QSPI Host Interface Using Quad SPI Connection

The QSPI Host Interface is powered by VCCIO1, which can accept power supply inputs of 1.8V, 2.5V or 3.3V. This allows the BT820 to match VCCIO1 with the MCU's I/O voltage.

# 4.5.1 QSPI Host Interface Protocol

In contrast to the QSPI host interface for the BT81x, which supports 22 bit addressing, the QSPI host interface for the BT820 supports 31 bit addressing, accommodating a larger memory map.

For writes to the BT820, the protocol will operate as in previous EVE revision such as the BT81x, with "WR-Command/Addr3, Addr2, Addr1, Addr0, DataX, DataY, DataZ, ...". The WR-Command is a '1' in the most significant bit in Addr3.

For reads from the BT820, the protocol has updated to "RD-Command/Addr3, Addr2, Addr1, Addr0, (poll for 0x01), 0x01, 0x0

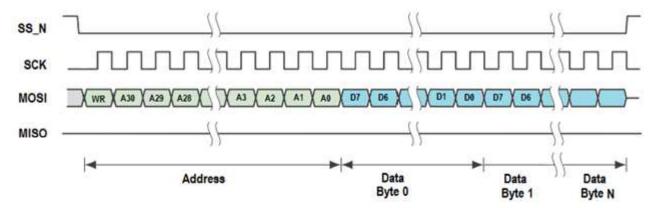

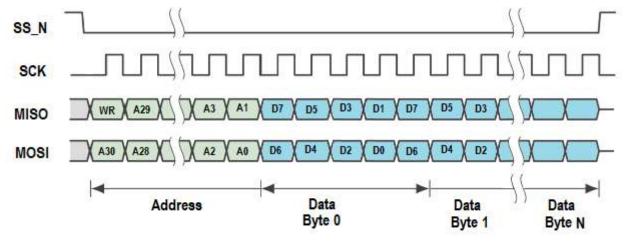

In SPI Single channel mode, the address and data are transmitted to the BT820 on the MOSI data port during a write transaction as shown in Figure 10.

Figure 10 - Write Transaction Using Single Channel Mode

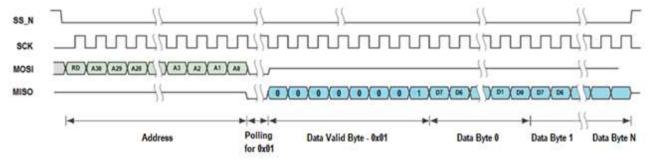

During read transactions the address is transmitted to the BT820 on the MOSI data port and the data is received on the MISO data port as shown in Figure 11. It also shows the polling for 0x01 and the data valid byte before the valid data.

Figure 11 - Read Transaction Using Single Channel Mode

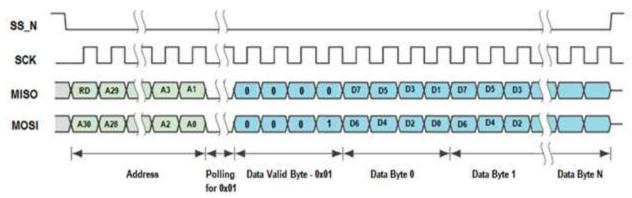

In SPI Dual channel mode, the address and data are transmitted on both the MISO and the MOSI data ports during write transactions with the most significant bit (MSB) transmitted on the MISO data port as shown in Figure 12.

Figure 12 - Write Transaction Using Dual Channel Mode

During read transactions, the MCU changes the data ports to input after the desired address is transmitted and polls for 0x01. Upon receiving 0x01, the next bytes onwards are the valid data bytes as shown in Figure 13.

Figure 13 - Read Transaction Using Dual Channel Mode

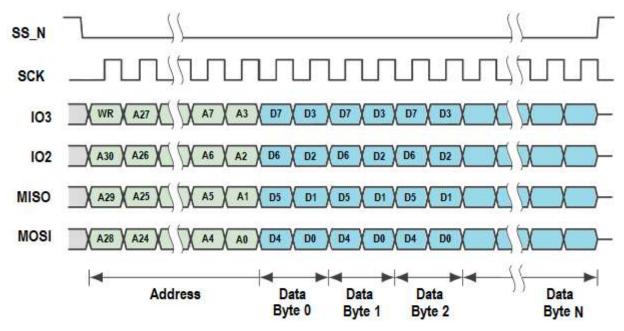

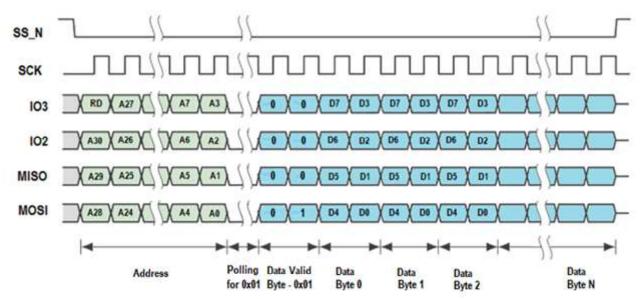

In SPI Quad channel mode, the transactions are similar to SPI Dual channel mode except for the additional IO3 and IO2 data ports. The address and data are transmitted on IO3, IO2 MISO and MOSI data ports with the most significant bit transmitted on IO3.

Figure 14 - Write Transaction Using Quad Channel Mode

Figure 15 - Read Transaction Using Quad Channel Mode

A transaction is considered to have started when SS\_N is driven to logic low and is considered to have ended when SS\_N is released to logic high. SS\_N high periods between transactions should have a minimum of 2 SCK cycles to ensure proper detection.

The transactions are word based, i.e., the data width must be in blocks of 32 bit when accessing the registers and the DDR memory of the BT820. Addressing to the registers and the DDR memory must also be word aligned, i.e., the last two bits of the received address is ignored.

In the case where the ports are bi-directional, a change of port direction will occur before 0x01 is clocked out of the BT820. Therefore, it is important that the MCU firmware controlling the SPI master changes the SPI master data ports direction to "input" after transmitting Addr0 and start polling for the data valid byte. BT820 will not change the port direction until it starts to clock out the data valid byte. The polling period will be used as a change-over period when neither the SPI master nor BT820 is driving the bus. The data ports must thus have pull-downs.

The QSPI Host Interface will reset all its data ports direction to input mode once SS\_N goes inactive.

Note that IO2 and IO3 data pins in the QSPI host interface are shared with GPIO0 and GPIO1. These pins take on the QSPI host interface data pins when it is configured to QSPI Quad channel mode. Otherwise, they default to GPIO0 and GPIO1. The application software might require the QSPI host interface to switch between different channel modes, including Quad channel mode. As the default pin type settings for the GPIOs are input with pull-up, the pin type settings for GPIO0 and GPIO1 should then be set to match the QSPI host interface settings. Leaving them in their default pull-up settings will cause unnecessary power leakage.

#### 4.5.2 Serial Data Protocol

The BT820 appears to the MCU as a memory-mapped SPI device. The MCU communicates with the BT820 using reads and writes to a large (2 Gbytes) address space. Within this address space are dedicated areas for graphics, audio, and touch control. Refer to BRT AN086 BT82X Series Programming Guide for detailed memory map. The MCU reads and writes the BT820 address space using the SPI transactions. Theses transactions are memory read, memory write and command write.

#### 4.5.3 Host Memory Read

For host memory read transactions, the MCU sends the 31 bit address with the MSB sets to '0'. This is followed by polling for the data valid byte. The BT820 responds with the data valid byte followed by valid data bytes.

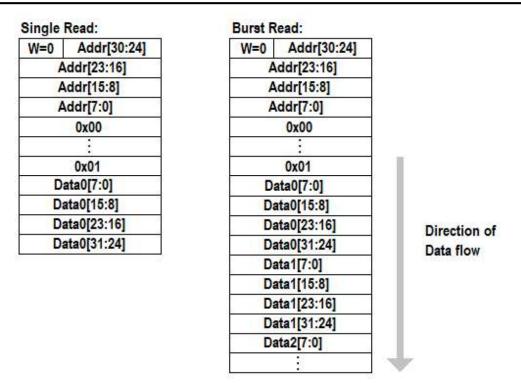

Figure 16 - Host Memory Read Transaction

The BT820 also supports memory burst read to increase the efficiency when accessing the internal registers and memories. The memory burst read are supported only in Single channel mode and Dual channel mode when accessing to the internal registers. Burst read in Quad channel mode is only supported when accessing to the DDR memory.

Figure 16 illustrates the direction of the data flow in a Single read transaction and a burst read transaction. The burst read transaction is enabled by default and can be disabled through register settings in the BT820. Refer to BRT AN086 BT82X Series Programming Guide for details on how to disable the burst read transaction.

When enabled, the BT820 auto-increments the address and pre-fetch the read data. The pre-fetched data is discarded if SS\_N is deactivated. In the event where there is an illegal addressing, BT820 will return an error code 0xDEADABBA.

When disabled, the BT820 will return the same data value until the SS\_N is deactivated.

#### 4.5.4 Host Memory Write

For host memory write transactions, the MCU sends the 31 bit address with the MSB sets to `1'. This is followed by the desired data to be written.

#### Single Write: **Burst Write:** W=1 Addr[30:24] Addr[30:24] W=1 Addr[23:16] Addr[23:16] Addr[15:8] Addr[15:8] Addr[7:0] Addr[7:0] Direction of Data0[7:0] Data0[7:0] Data flow Data0[15:8] Data0[15:8] Data0[23:16] Data0[23:16] Data0[31:24] Data0[31:24] Data1[7:0] Data1[15:8] Data1[23:16] Data1[31:24] Data2[7:0]

Figure 17 - Host Memory Write Transactions

The BT820 also supports memory burst write transactions. Similar to the burst read, burst writes are supported only in Single channel mode and Dual channel mode when accessing to the internal register. Burst write in Quad channel mode is only supported when accessing to the DDR memory.

Figure 17 illustrates the direction of the data flow in Single write transaction and in a burst write transaction. The burst write transaction is always enabled. The MCU writes data until it deactivates the SS\_N. The address is auto-incremented as long as the SS\_N is active. The write data is expected to be in blocks of 32-bit. Any incomplete data is discarded when SS\_N deactivates.

#### 4.6 Host Commands

BT820 provides a set of host commands for system configurations. The host command can only be executed when the QSPI host interface is operating in Single channel mode. They will be ignored when it is in either Dual or Quad channel modes.

The host command uses a special SPI sequence to program the system configuration. The system configuration registers programmed by the host command should only be updated when the system is in an idle state, i.e., when BT820 is not in ACTIVE state and they retained their settings when the system enters lower power states. These registers are only reset when POR or RST\_N pin is activated, or when power is lost.

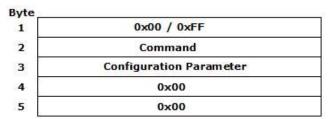

Figure 18 - Host Command Transaction

The SPI sequence for the host command is shown in Figure 18.

To write to the system configuration, the MCU sends 0xFF followed by the Command and Configuration parameter of the desired system configuration, and two bytes of trailing `0'.

The ACTIVE Command has a special sequence where the MCU sends 0x00 across all 5 bytes. Refer to section 4.17.4.1 for more information about the ACTIVE command.

Refer to BRT AN086 BT82X Series Programming Guide for detailed descriptions of the host commands.

# 4.7 Quad SPI Flash Interface

The BT820 implements a Quad SPI (QSPI) Flash Interface that acts as a QSPI master to connect to an external NOR / NAND flash memory device. Application specific graphics assets such as Unicode fonts and images can be stored in the flash memory. The BT820 graphics engine can read these gaphics assets directly and write them to the main memory without going through the external MCU, thus significantly off-loading the MCU from feeding the display contents.

The BT820 supports XIP (execute-in-place) operations and Discoverable Parameters (SFDP) register when using NOR flash. The interface work at the system clock speed in 4-bit mode, providing a maximum data read throughput of 288Mbit/s at 72 MHz system clock.

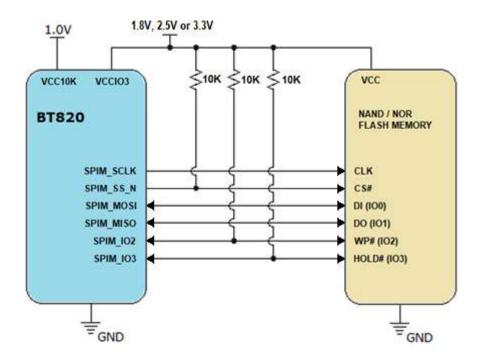

Figure 19 illustrates a typical connection for Flash Memory device.

Figure 19 - Typical Connection for Flash Memory

The BT820 supports a separate I/O voltage (VCCIO3) for QSPI flash interface allowing the use of a wider range of flash devices without affecting the other interfaces.

| Brand    | Model              | JEDEC ID | Description               |

|----------|--------------------|----------|---------------------------|

|          | AS5F31G04SND-08LIN | 52 25 52 | 3.3V, 1Gbit, QSPI, 120MHz |

|          | AS5F32G04SND-08LIN | 52 2E 52 | 3.3V, 2Gbit, QSPI, 120MHz |

|          | AS5F34G04SND-08LIN | 52 2F 52 | 3.3V, 4Gbit, QSPI, 120MHz |

| Alliance | AS5F38G04SND-08LIN | 52 2D 52 | 3.3V, 8Gbit, QSPI, 120MHz |

|          | AS5F12G04SND-10LIN | 52 8E 52 | 1.8V, 2Gbit QSPI, 100MHz  |

|          | AS5F14G04SND-10LIN | 52 8F 52 | 1.8V, 4Gbit, QSPI, 100MHz |

|          | AS5F18G04SND-10LIN | 52 8D 52 | 1.8V, 8Gbit, QSPI, 100MHz |

| Winbond  | W25N01GV series    | EF AA 21 | 3.3V, 1Gbit, QSPI, 104MHz |

|          | W25N01KV series    | EF AE 21 | 3.3V, 1Gbit, QSPI, 104MHz |

| Micron   | MT29F2G01ABBGDWB   | 2C 25 2C | 1.8V, 2Gbit, QSPI, 83MHz  |

Table 6 - Supported NAND Flash Devices

Table 6 lists the supported NAND Flash devices. Note that these are the only NAND flash devices that are supported by BT820.

| Brand    | Model            | Туре | Description                               |

|----------|------------------|------|-------------------------------------------|

| Winbond  | W25Q128JV series | NOR  | IC NOR Flash, 3.3V, 128Mbit, QSPI, 133MHz |

| Micron   | M25QL128 series  | NOR  | IC NOR Flash, 3.3V, 128Mbit, QSPI, 133MHz |

| Micronix | MX25L256 series  | NOR  | IC NOR FLASH, 3.3V, 256Mbit, QSPI, 120MHz |

| ISSI     | IS25LP256        | NOR  | IC NOR FLASH, 3.3V, 256Mbit, QSPI, 133MHz |

Table 7 - Supported NOR Flash Devices

Table 7 lists the supported NOR Flash Devices. The devices listed in Table 7 represent samples for each family test compatible with BT820.

In certain flash memory device such as the W25N01GVZEIG from Winbond, the HOLD# and IO3 signals share the same pin, as to the WP# and IO2 signals. During Quad operations, the HOLD# pin functions as a data I/O pin, temporarily disabling the hold function until the operation completes. Therefore, an external pull-up resistor is necessary to prevent the HOLD# pin from floating.

#### 4.8 SD Card Host Controller

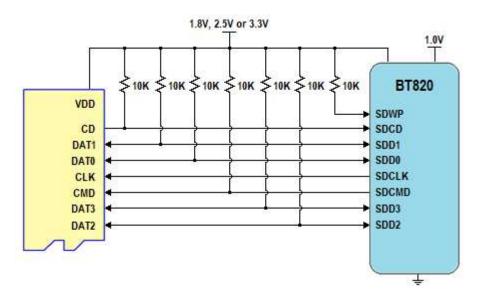

The BT820 implements a SD Card Host Controller offering access to external large capacity non-volatile memory. The SD Card host controller operates up to 36MHz and supports DDR50 and SDR50 SD modes. It is powered by VCCIO4, which can be configured to 1.8V for low voltage signalling without affecting the other interfaces.

Figure 20 illustrates a typical connection for the SD Host controller.

Figure 20 - Typical connection for SD Host Controller

# 4.9 Touch Engine and Interface

The BT820 is compatible with various touch controllers, including capacitive touch controller ICs from FocalTech, Goodix, Ilitek and Sitronix, as well as resistive touch controller ICs from TI and Microchip.

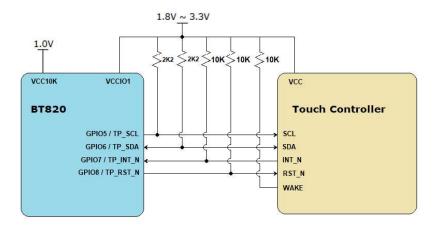

The Touch Engine of the BT820 communicates with the external touch device through an I2C interface. The I2C interface supports standard mode, up to 100KHz and fast mode, up to 400KHz. The Touch Engine supports auto-discovery of the attached external touch devices. Up to 5 touches can be reported and stored in the BT820 registers.

Figure 21 illustrates the typical Touch Screen Connection.

Figure 21 - Typical Touch Screen connection

Note that the touch interface of BT820 is powered by VCCIO1 that also powered by QSPI Host Interface. Level shifters are required if the voltage level of the external touch panel does not match the MCU's I/O voltage.

Table 8 lists the capacitive touch controllers and Table 9 lsts the resistive touch controllers which are supported by BT820 auto-discovery feature. Note that the particular models listed in this table represent samples for each family tested compatible with BT820. Other models not listed are expected to work if their protocol is compatible to the listed controller.

| Brand     | Models                                | I2C Address |

|-----------|---------------------------------------|-------------|

|           | FT5x06 series: FT5206, FT5306, FT5406 |             |

|           | FT5x16 series: FT5316                 |             |

| FocalTech | FT5x26 series: FT5426                 | 0x38        |

|           | FT5x36 series:                        |             |

|           | FT5x46 series:                        |             |

| Goodix    | GT9xx series:                         | 0x5D        |

| Ilitek    | ILI2511                               | 0x41        |

| Sitronix  | ST1633i                               | 0x55        |

Table 8 - List of Supported Capacitive Touch Controller

| Brand     | Models  | I2C Address |

|-----------|---------|-------------|

| Microchip | AR1021  | 0x4D        |

| TI        | TSC2007 | 0x48        |

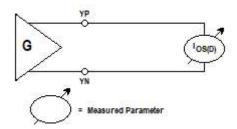

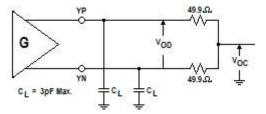

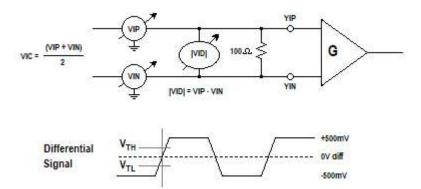

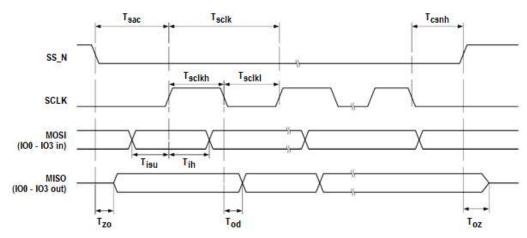

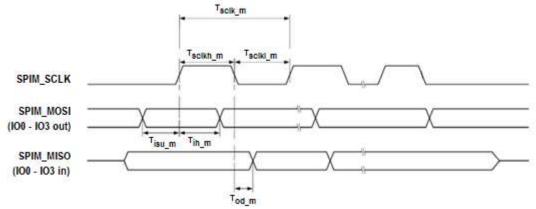

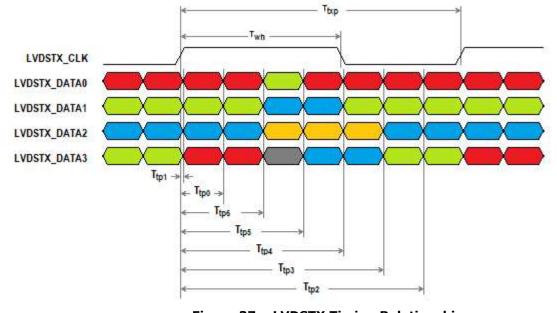

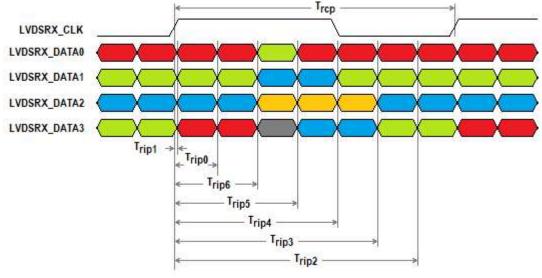

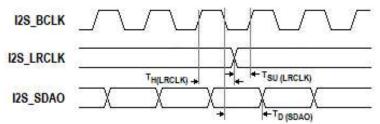

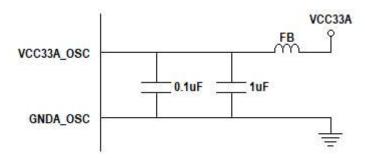

Table 9 - List of Supported Resistive Touch Controller